Table of Contents

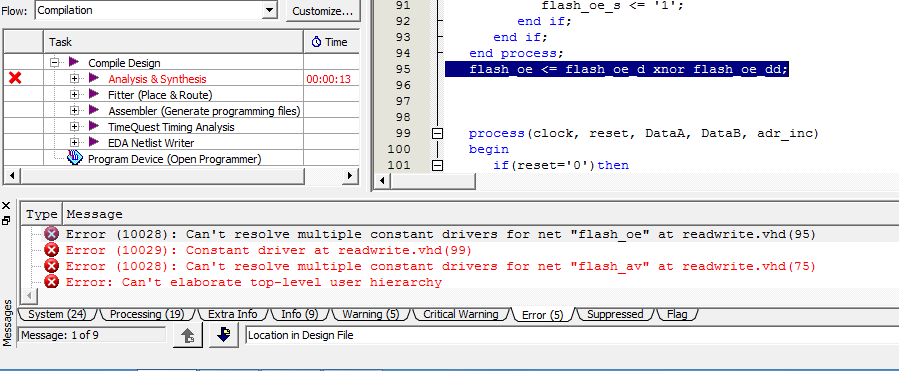

In this user guide, we are going to describe some of the possible causes that might cause the Verilog error 10028 and then suggest some possible fixes that you can try to fix the problem.

Updated

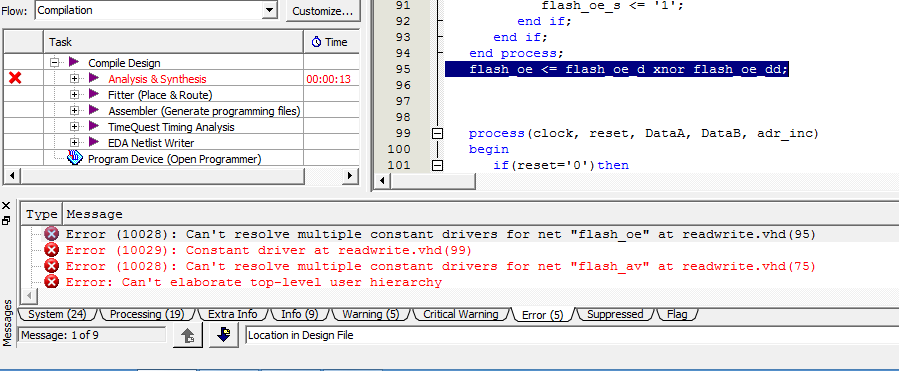

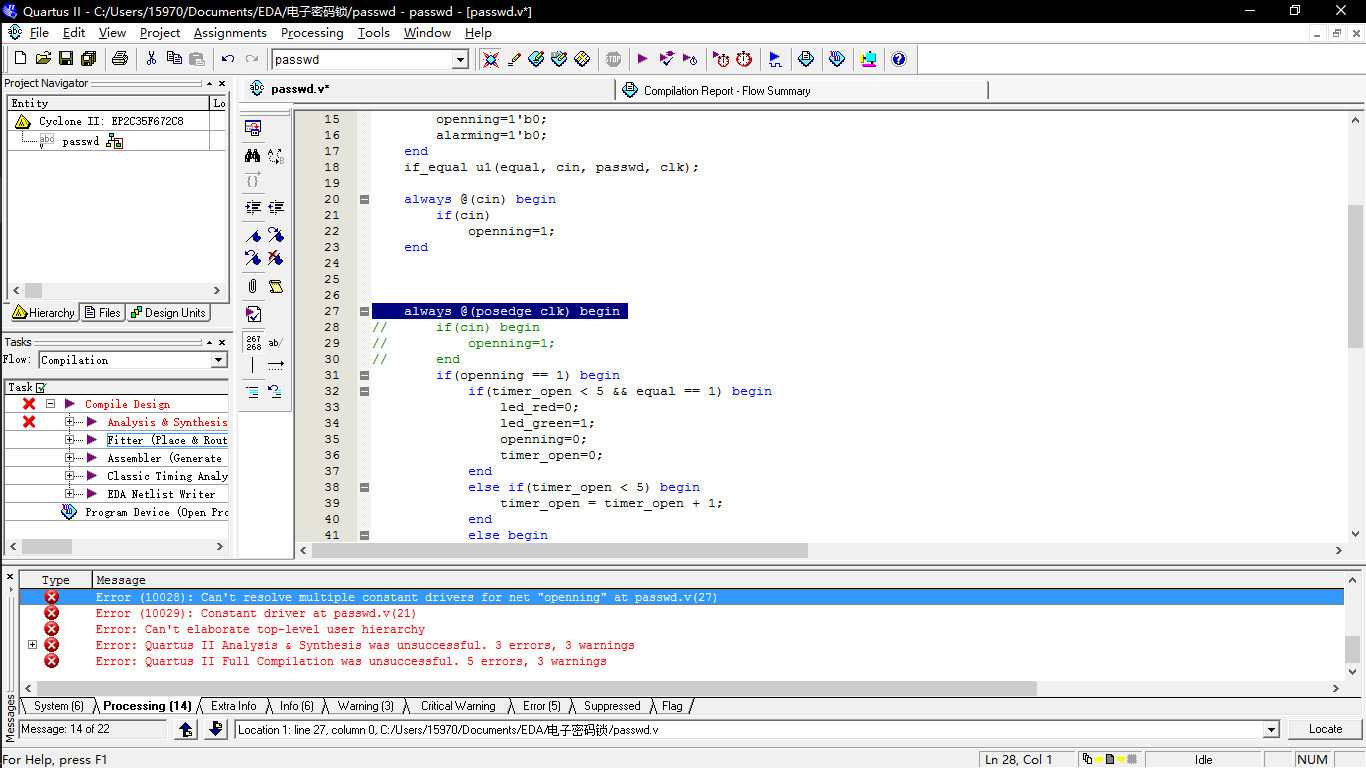

I am trying to write code that detects the rising edge of a noise signal and then increments it by 5 clocks. I am getting various errors and do not understand what they mean. I think I am missing a basic understanding of some VHDL concepts, but unfortunately internet research hasn’t helped me much. I still don’t know what are the valid actions of our own software.

In my I-code, I currently have a load edge sensor in the first process that drives Dout high. The run second additionally checks if Dout is high, so it counts from 5 as the path to 0 and sets Dout to 0 so you can be logically low.

Error (10028): Unable to definitively resolve the number of drivers for network “number [2]” in rise_ext. (10028). (10028): vhd (31)

Error Unable to resolve multiple persistent drivers for web account “account [1]” in rise_ext.vhd (31)

Error (10028): infinite number of drivers for rise_ext.vhd (31) net “account [0]” could not be resolved

Error (10028): Multiple persistent drivers could not be resolved, h To get a clear “doubt” in rise_ext.vhd (31)

Updated

Are you tired of your computer running slow? Annoyed by frustrating error messages? ASR Pro is the solution for you! Our recommended tool will quickly diagnose and repair Windows issues while dramatically increasing system performance. So don't wait any longer, download ASR Pro today!

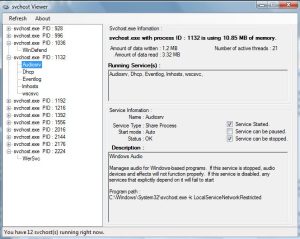

Error: Failed to parse and synthesize the 32-bit version of Quartus II. 7 errors, 2 warnings Error: Maximum virtual memory value: 326 MB Error: Processing completed: Sat Jan 19 13:13:38 2014 Error expired: one period: 00:00:04 Error: Total CPU time (across all processors): 00:00:02

Error (293001): Full compilation of Quartus II failed. 9 sheets, 2 warnings

is the rise_ext state port (clk: slice; resetN: total; din: in bits; count: the range of integers in the buffer, from two to 6; I doubt: buffer bit);end rise_ext;Arc_rise_ext architecture by rise_ext Signal s1, s2: during;begin Process (resetN, clk) begin as if resetN = '0' then from <= '0'; Number <=; 5 elsif clk'event and additionally clk = '1', then s1 <= noise; s2 <= s1; doubt <= far from s1 and s2; End if; The final process; process (clk, doubt) begin if clk'event is higher than clk = '1' then if maybe doout = '1' then if the number> 6, then account <= account - 1; anotherfrom <= '0'; account <=; a five-pointed tail, however; End if; cure when; complete the whole process;End arc_rise_ext;

I changed all exact record types to std_logic and did the action, I still get these errors ...

Library

ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Object - rise_ext mov (clk: in std_logic; resetN: here in std_logic; Noise: in std_logic; count: a range of integers from 0 to 6; I doubt: std_logic buffer);end rise_ext;Arc_rise_ext architecture by rise_ext Signal s1 - s2: logic_std;begin summary (resetN, clk) begin if resetN = '0' then from <= '0'; count <= 12; elsif rise_flank (clk) then s1 <= din; s2 <= s1; I doubt <= not s1, but s2; End if; The final process; Progress (clk) begin if amount_bord (clk) then in cases where doubt = '1' then quantity <= 5; Party if; End if; The final process; Routine (clk) begin if amount_bord (clk) then if you think count = 0 then Material <= 6; from <= '0'; another let <= count - 1; End if; Must finishXia; End the processes;End arc_rise_ext;

Speed up your computer today with this simple download.

Verilog-Fehler 10028

Erro Verilog 10028

Verilog Error 10028

Error De Verilog 10028

Błąd Veriloga 10028

Errore Verilog 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028

Erreur Verilog 10028