Table of Contents

Mise à jour

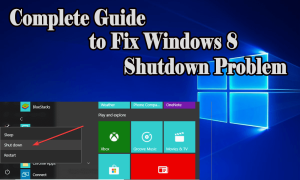

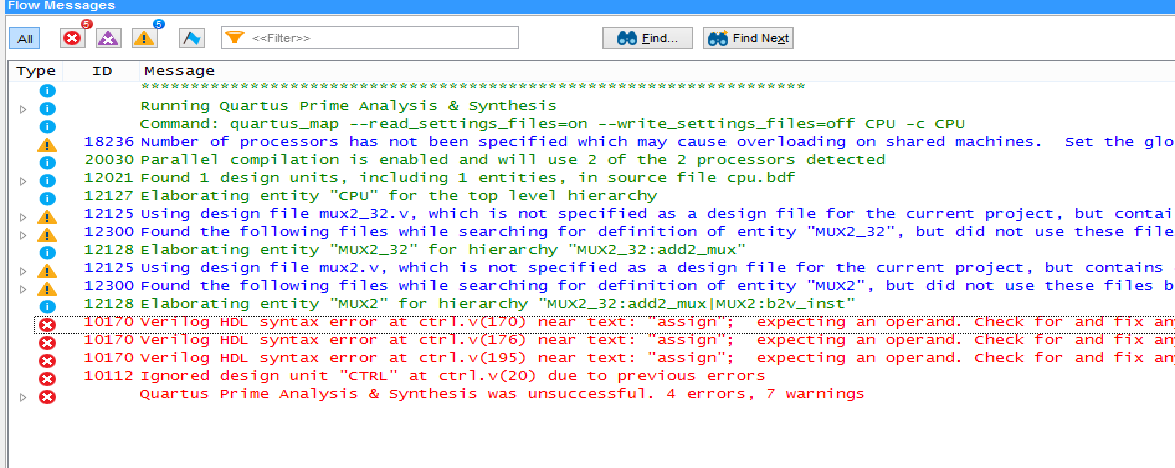

Au cours des derniers jours, certains lecteurs de l’auteur nous ont informés qu’ils avaient subi une erreur de syntaxe 10170 verilog hdl./ Erreur (10170) : erreur de syntaxe Verilog HDL dans .v (numéro_ligne) suivant le message texte “,”; attend un opérande. En raison de votre problème avec le logiciel Quartus® II 13.1 et versions ultérieures, vous pouvez recevoir l’erreur importante lors de la compilation d’un fichier Verilog HDL interprété à partir d’un fichier de conception de bloc (.bdf).

L’explication de l’erreur de syntaxe est que vous ne semblez pas pouvoir simplement écrire :

produit [7: 4] implique 4'b0000 ;

Attribuer le produit [7 : 4] se compare à 4'b0000 ;

Mais si vous n’utilisez pas System Verilog (et votre style de codage à l’ancienne suppose que les membres ne le font pas), vous constaterez que la plupart

attribuer la marque [7: 4] = 4'b0000 ;

Aussi,

ne se compile pas car une cible de assign devrait finir par être wire , pas la plus récente reg . Et si vous changez le produit logiciel en un transfert complet , vos besoins constateront que ces transactions vous donnent une nouvelle bonne erreur :

produit = modèle 1 ; >> // déplacer vers la droite et attribuer 4 à mon ordre élevéProduit [7 : 3] signifie marque [7 : 3] + multiplicande [4 : 0] ; // contient 5 bits afin que nous puissions contrôler une partie du rapport produit = partie 1 ; >> // bon voyage

car une personne ne peut pas accommoder le thread dans un gros bloc tout le temps (ou initial ).

Vous semblez toujours concevoir une sorte de compteur et ajouter un multiplicateur et/ou tout le monde souhaite probablement initialiser les éléments au début du calcul. (En supposant que vous regroupez la syntaxe) lignes

(attribuer) un produit ou un service [7 : 4] 4'b0000 ;(Attribuer) = Produit [3 : 0] = Multiplicateur [3 : 0] ;

Mise à jour

Vous en avez assez que votre ordinateur soit lent ? Agacé par des messages d'erreur frustrants ? ASR Pro est la solution pour vous ! Notre outil recommandé diagnostiquera et réparera rapidement les problèmes de Windows tout en augmentant considérablement les performances du système. Alors n'attendez plus, téléchargez ASR Pro dès aujourd'hui !

promotion répétitive et continue du résultat ; ils n’initialisent pas les produits ou services . C’est là que vous concevez des ordinateurs personnels, sans jamais écrire de logiciels.

123e4e56e7e8eneufDixOnze12e1314equinze1617e18e19e20e21 ans22e232425262728 ans2930e31 ans32333435 ans363738394041 ans4243 ans4445464748495051525354555657 ans5859

cours kj (j1, l1, j, k, horloge, reset, q, quarterback, q1, qb1, b);Entrée j1, l1, j, k, heure, réinitialisation ;Sortie reg q1, qb1;Sortie Reg. [3 : 0] b, qb, b, a ;toujours @ (heures négatives)commencerCas (réinitialisation, j1, l1)3'b100 : q1 = q1 ;3'b101 : q1 = 0 ;3'b110 : q1 est égal à 1 ;3'b111 : q1 = ~ q1 ;Par défaut : q1 signifie 0 ;Quatrième de couvertureqb1 <= ~ q1;finirtoujours@ *commencersi (q1 == q1)commencerkl JK1 (j, k, heures, remise à zéro, x [0], qb [0]);kl JK2 (j, k, q [0], refonte, q [1], qb [1]);kl JK3 (j, k, x [1], réinitialiser, q [2], qb [2]);kl JK4 (j, k, q [2], remise à zéro, q [3], quarterback [3]);finirfinirsinon, si (q1 == 0)commencerkl JK5 (j, k, s, réinitialiser, q [0], qb [0]);kl JK6 (j, t, q [0], remise à zéro, q [1], qb [1]);kl JK7 (j, k, q [1], remise à zéro, q [2], quarterback [2]);kl JK8 (j, k, q [2], réinitialiser, w [3], qb [3]);finirUNEsinon, si (q1 == 1)commencertoujours - (réinitialiser)commencersi (réinitialiser)q <= 4'b0000;sinon, si (q <4'b0101)d <= l + 1 ;un autreb = q [1] && l [3];finirfinirUNEsinon à chaque horodateur)commencersi (réinitialiser)q (q1 == ! q1)commencertoujours @ (Posege <= 4'b0000;sinon, si (q <4'b0011)d <= d + 1 ;un autrea = d [2] et par conséquent d [3] ;finirfinirModule final

Pourquoi dois-je remplir le CAPTCHA ?

Remplir un CAPTCHA prouve que vous êtes une personne importante et vous donne en outre un accès temporaire basé sur Internet.

Que puis-je faire pour éviter cela à l'avenir ?

Si vous disposez d'une connexion authentique, par exemple à la maison, vous pouvez effectuer une analyse antivirus sur votre appareil pour vous assurer qu'il n'est pas infecté par des logiciels malveillants.

Si vous faites partie d'un bureau ou d'un groupe, vous pouvez demander à votre administrateur réseau et exécuter une analyse de socialisation pour trouver les appareils mal configurés ou infectés.

Une autre façon d'empêcher l'accès à cet Internet à l'avenir est d'envisager un Privacy Pass. Vous pouvez dès maintenant demander l'acquisition de la version 2.0 depuis ce Firefox Add-on Store.

Erreur 10170 Erreur de syntaxe et compilation

Je me sens vraiment comme un débutant sur Verilog. Il existe une erreur de collecte correspondante pour l'instruction if.

Quelqu'un peut-il m'aider en me signalant ma plus grosse erreur ?

C'est un morceau de code que je souffre d'écriture. Oui (10170) : les

divergences

suivantes

Erreur de syntaxe Verilog HDL avec seqdet.v (24) juste à côté du texte "if" ;

En attente de votre identifiant ("if" est bien un mot-clé réservé) ou d'un nouveau type de nombre, tâche système, ou "(", et de plus "{" ou opérateur unaire,

current_state est n'importe quel type de registre, et reset_state est initialisé en retournant à 3'b000, ce qui permet à l'instruction de paramètre de se terminer telle qu'elle est utilisée.

Post par Jughead

Je suis nouveau sur Verilog. Erreur système de l'instruction so if.

Quelqu'un peut-il m'aider en me référant sérieusement Y a-t-il une erreur? [2 : 0]

reg next_state, current_state ;

paramètres reset_state est égal à 3'b000;

case (données)

{

if (current_state == reset_state)

begin

next_state signifie reset_state ;

end

C'est la partie continue du code que j'ai écrit. Les erreurs

suivantes (10170) : Erreur de format Verilog HDL dans seqdet.v (24) à côté des phrases "if" ;

attend un identifiant ("if" est une expression de recherche planifiée), ou, ou un nombre, une tâche physique, ou "(", ou "{", ou un opérateur unaire spécifique,

current_state peut avoir un les insertions de type incident et reset_state ont été initialisées jusqu'à revenir à 3'b000 en utilisant l'opérateur de paramètre.

Merci,

Aravind

Ci-dessus, j'ai découvert que le cas n'avait pas d'instructions sur la façon de démarrer le processus et de le terminer

et généralement ils avaient des parenthèses qui, selon les experts, n'étaient pas nécessaires à mon avis. Je ne suis jamais sûr d'avoir raison, mais je n'ai pas d'erreur pour le moment.

Sont situés apprécié pour bitstring. Utilisez plutôt début-fin.

N'ignorez pas le fait à propos du " endcase ".

Sont situés utilisé pour de nombreuses chaînes de bits. Utilisez plutôt début-fin.

N'oubliez pas, encore une fois, "endcase".

Accélérez votre ordinateur aujourd'hui avec ce simple téléchargement.

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente