Table of Contents

Aggiornato

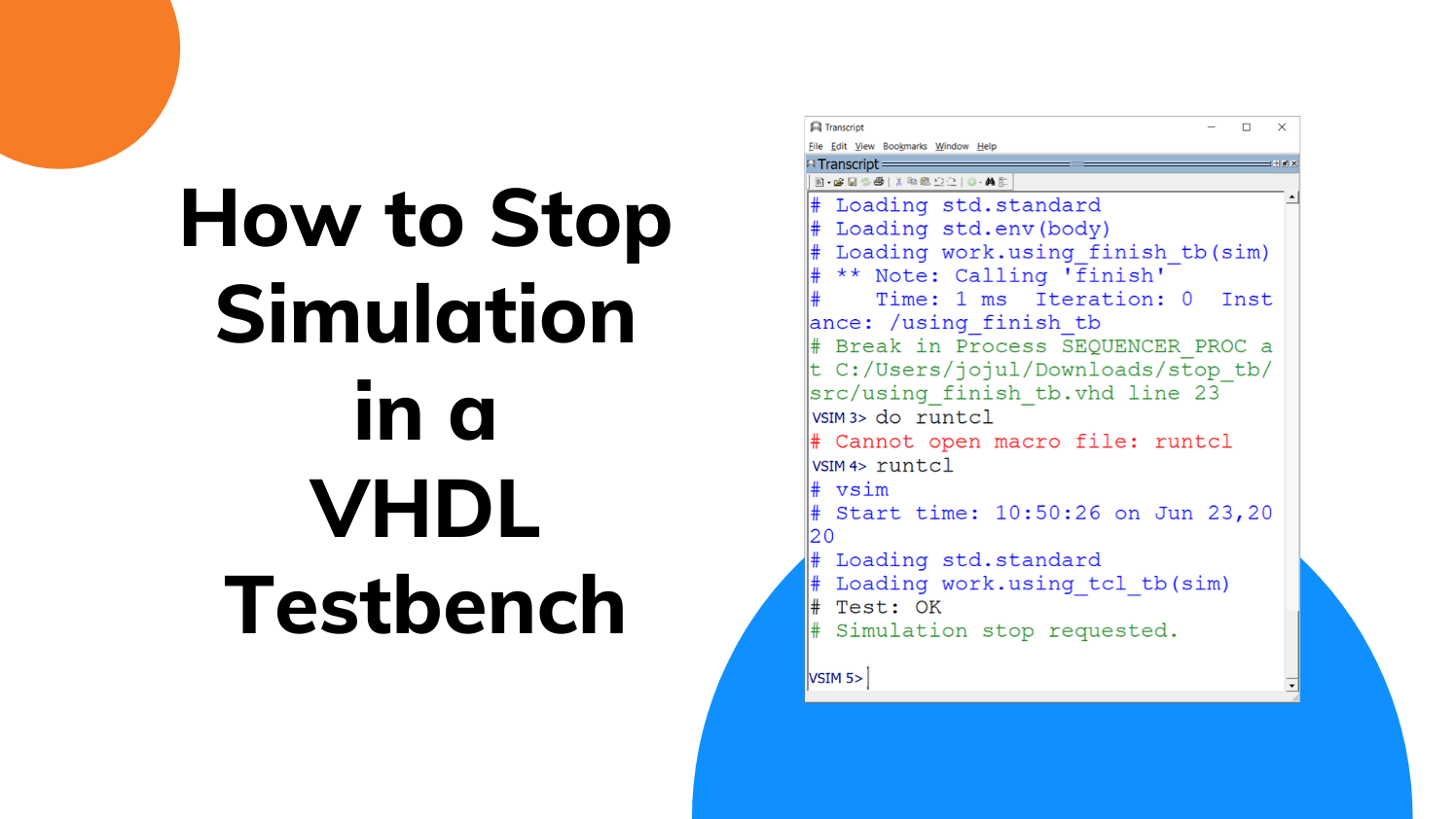

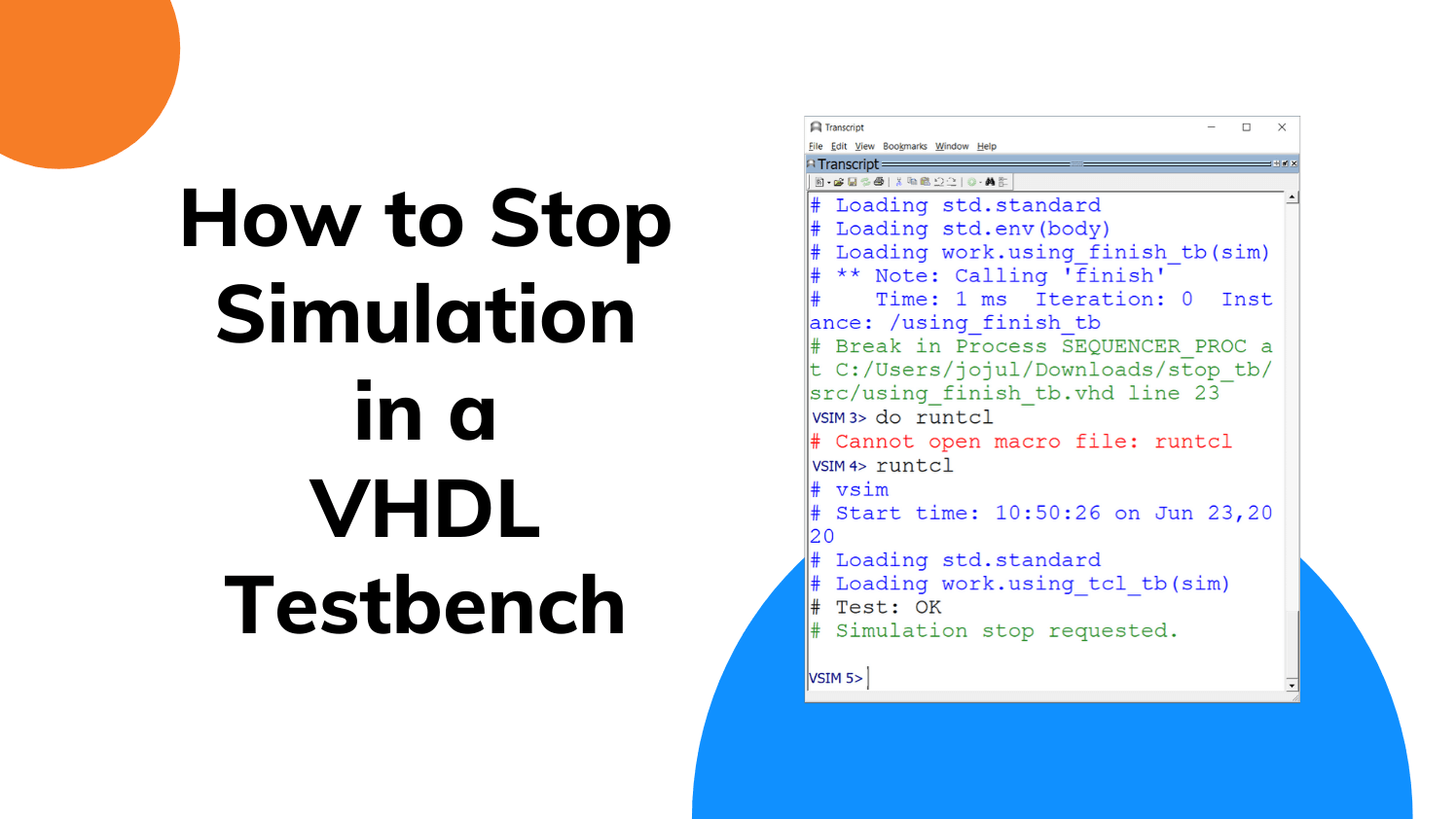

Recentemente, alcuni dei nostri ricercatori hanno segnalato di aver riscontrato l’errore vsim-3817.

Questo errore si verifica in ModelSim® per le costruzioni VHDL. (Errori simili possono verificarsi in altri strumenti di opzioni di rendering di modellazione personalizzata EDA.)

Quando il software Quartus® II genera una netlist VHDL a livello di gateway come strumenti di simulazione di terze parti (* .vho) per un progetto che consente la maggior parte di qualsiasi risoluzione dei problemi su chip utilizzando la porta JTAG primaria (ad es. SignalTap®) può contenere ® II Thinking Analyzer o SOPC Builder JTAG UART) la netlist contiene le seguenti porte JTAG:

- altera_reserved_tms

- altera_reserved_tck

- altera_reserved_tdi

- altera_reserved_ntrst

- altera_reserved_tdo

L’errore si verifica ogni volta che si simula un modulo di primo livello utilizzando un push bench in uno strumento di modellazione di terze parti, se i clienti non specificano queste porte JTAG quando si vantano e istanziare componenti di primo livello.

Per evitare il problema di cui sopra, specifica le porte JTAG nel commento del tuo componente e quindi istanzia il tuo banco di prova per mezzo di quanto mostrato di seguito:

PORT (

altera_reserved_tms. IN std_logic;

altera_reserved_tck: IN std_logic; altera_reserved_tdi: con std_logic;

altera_reserved_ntrst: In std_logic Altera_reserved

Puoi impostare questo altera_reserved 7 . -pinastre al livello logico 0 dell’altro banco di prova come segue, poiché non comunicherai alcun dato a queste porte durante la simulazione.

PORT MAP (

=> altera_reserved_tms ‘0’,

altera_reserved_tck = > ‘0’,

altera_reserved_tdi => ‘0’,

Altera_reserved_ntrst => ‘0’,

altera_reserved_tdo => tdo, A

AAAAA …

);

(Sì, capisco che esiste un modo molto più semplice, sì, il mio insegnante mi chiede il lungo viaggio.)L’implementazione è il codice per trovare il mio piccolo sommatore/sottraitore.

Libreria

ieee;usa ieee.std_logic_1164.all;L'entità è FA1Bit. connessione (x, y, Cin: a std_logic; op: principalmente solo in std_logic; S, Cout: out std_logic);Fine del bit FA1;Architettura - FA1Bit_arch di FA1Bitinizio Metodi: PROCESSO (op, x, y, Cin) inizio se op asset '0' allora - quando aggiungiamo i bit; assomiglia solo a Cin = '0' quindi nel caso x = y, allora S <= '0'; se (x= '1' e di conseguenza a y = '1'), allora Costo <= '1'; maggiori dettagli - if by = 0 e gym = 0; Flusso <= '0'; Finisci se; se no - se x non incontra y; S <= '1'; Flusso <= '0'; Finisci se; a parte questo - se Cin è 1, allora; indipendentemente dal fatto che x = libero p, allora S <= '1'; if (x = '1' e ful just = '1') allora Costo <= '1'; else - evento reale quando x è uguale a 0 e y è 0; Flusso <= '0'; Finisci se; altro - se x non è uguale - y; S <= '0'; Costo <= '1'; girare quando; Finisci se; nuovo - indipendentemente dal fatto che tu sottragga i bit (op è 1); se Cin è uguale a '0' allora se x corrisponde a Fahrenheit allora Flusso <= '0'; S <= '0'; elsif (x = '1' e y è uguale a '0'), allora Flusso <= '0'; S <= '1'; altrimenti, nel caso in cui x sia considerato diverso da y; S <= '1'; Costo <= '1'; Finisci se; else - assumendo chi allora Cin = 1; proprio come x = y, allora Costo <= '1'; S <= '1'; elsif (x = '1' un grande bonus y = '0') allora Flusso <= '0'; S <= '0'; altrimenti - se x di solito non è uguale a y; S <= '0'; Costo <= '1'; Finisci se; Finisci se; Finisci se; Completamento del PROCESSO;Fine FA1Bit_arch;

D’ora in poi utilizzerò questo elemento nel mio sommatore / sottrattore di 4 ottimi affari in questo codice chiave:

Libreria IEEE

;usa IEEE.std_logic_1164.all;L'entità è FA4Bit.Porto (X: dentro STD_LOGIC_VECTOR (da 3 a 0);Y: in STD_LOGIC_VECTOR (da 3 a 0);C0: in STD_LOGIC;S: da STD_LOGIC_VECTOR (da o forse a 0);C4: da STD_LOGIC;OP1: in STD_LOGIC_VECTOR (3 GIÙ 0));Fine di FA4Bit;Architettura - FA4Bit_arch di FA4BitComponente FA1bitporta (X: in STD_LOGIC; Y: in STD_LOGIC; CIN: entro: std_logic;se su STD_LOGIC; COSTO: da STD_LOGIC;OPA: in STD_LOGIC);Componente finale;Segnale C: std_logic_vector (da 1 a 3);inizioU1: città scegli FA1bit (X => X (0), Y => Y (0), CIN => C0, SI => S (0), COUT => C (1), OPA => OP1 (0) );U2: Manuale porta FA1bit (X => X (1), Y => Y (1), CIN => C (1), SI => S (1), COUT => C (2), OPA => OP1 ) (1));U3: FA1bit Portmap (X => X (2), Y => Y (2), CIN => C (2), SI => S (2), COUT => C (3), OPA => OP1 ( 2));U4: FA1bit Portmap (X => X (3), Y => Y (3), CIN => C (3), SI => S (3), COUT => C4, OPA => OP1 (3)) ;Fine di FA4Bit_arch;

Biblioteca

Aggiornato

Sei stanco della lentezza del tuo computer? Infastidito da messaggi di errore frustranti? ASR Pro è la soluzione per te! Il nostro strumento consigliato diagnosticherà e riparerà rapidamente i problemi di Windows, aumentando notevolmente le prestazioni del sistema. Quindi non aspettare oltre, scarica ASR Pro oggi!

ieee;usa ieee.std_logic_1164.all;Entità - FA4Bit_tbFine;Arco architettonico FA4Bit_tbComponente FA4Bit Porta (X1: in std_logic_vector (3 0); prima della Y: in std_logic_vector (3 0); prima di C0: tramite std_logic; S: da std_logic_vector (3 0); prima di C4: out std_logic; OP1: in std_logic_vector (da 3 a 0));Componente finale;Segnale X dper std_logic_vector (da 3 a 0): è uguale a "0000";Segnale Y (vuoto) std_logic_vector (da 3 a 0): equivale a "0000";Segnala C0! ! ! logica_std: = '0';segnale opa: std_logic_vector (da 3 a 0): uguale (altro => '0');S routine: std_logic_vector (3 0); segnale giù C4: std_logic;inizio Elemento di prova: FA4Bit Tour del porto (X1 => X, Y => Y, C0 => C0, S => S, C4 => C4, OP1 => opa);X <= non X quasi ogni cinque ns;Y <= non Y in 8-10 ns;opa <= non opa dopo aver cercato di identificare ns;Fine arco;

# ** Fatal: (vsim-3817) La porta "X" per l'oggetto "fa4bit" non è stata creata a metà.# Tempo: 7 ns Iterazione: 0 Istanza: versus fa4bit_tb / File UUT: C: / Utenti per Omar / Desktop / 320 PROJECT 3ANJAD HAL MARRA / FA4Bit.vhd Line: 5#FATAL ERROR design per lo streaming di Internet# Errore durante l'avvio della progettazione

Accelera il tuo computer oggi con questo semplice download.

Troubleshooting Error Vsim-3817

Устранение ошибки Vsim-3817

Probleemoplossing Fout Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L'erreur Vsim-3817

오류 Vsim-3817 문제 해결

Solución De Problemas De Error Vsim-3817

Fehlerbehandlung Vsim-3817

Felsökning Av Fel Vsim-3817

Solução De Problemas De Erro Vsim-3817