Table of Contents

Bijgewerkt

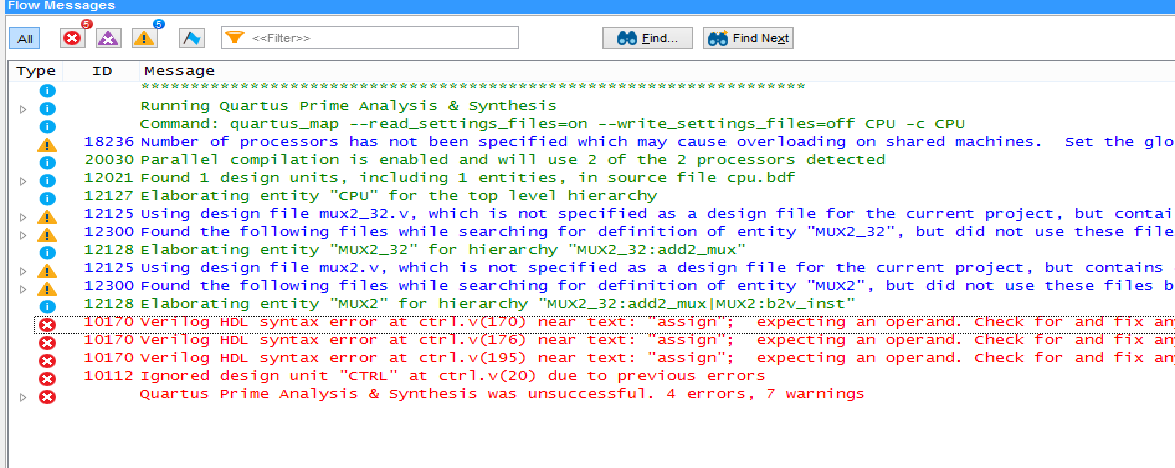

Gewoonlijk hebben enkele van onze lezers de afgelopen dagen ons laten weten dat ze formaatfout 10170 verilog hdl zijn tegengekomen./ Fout (10170): Verilog HDL-syntaxisfout in .v (regelnummer) naast artikelbericht “,”; verwacht een operand. Vanwege uw nieuwe probleem met Quartus® II-software type 13.1 samen met hierboven, kunt u de volgende foutmelding krijgen dat bij het compileren van een Verilog HDL-bestand dat is geconverteerd van een gloednieuw blokontwerpbestand (.bdf).

De reden voor de syntaxisfout is dat je niet zomaar het volgende kunt maken:

product [7: 4] = 4'b0000;

Product toewijzen [7: 4] komt voor u overeen met 4'b0000;

Maar als u System Verilog niet gebruikt (en uw ouderwetse coderingsstijl gaat ervan uit dat clients dat niet doen), zult u denken dat de meeste < /p>

product toewijzen [7: 4] betekent 4'b0000;

Ook

compileert niet omdat het doel van assign netsnoer moet zijn, niet de meest recente reg . En als je het product verandert om echt een volledige overboeking te doen, krijg je dat deze transacties je een foutmelding geven:

product = model 1; >> // rechts invullen en 0 toewijzen aan onze eigen hoge ordeProduct [7: 3] betekent product [7: 3] + vermenigvuldigtal [4: 0]; // voeg 5 elementen toe zodat we het rapport kunnen controleren

voedingssupplement = deel 1; >> // naar rechts manoeuvreren

omdat een persoon niet kan overeenkomen met plaats in een groot altijd (of initiaal ) blok.

U lijkt altijd een soort offset te ontwerpen en een vermenigvuldiger te plaatsen en/of u wilt waarschijnlijk het product initialiseren aan het begin van de berekening. (Ervan uitgaande dat u groepssyntaxis wordt) regels

(toewijzen) productservice [7: 4] 4'b0000;(Toewijzen) = Product [3: 0] betekent Vermenigvuldiger [3: 0];

Bijgewerkt

Bent u het beu dat uw computer traag werkt? Geërgerd door frustrerende foutmeldingen? ASR Pro is de oplossing voor jou! Onze aanbevolen tool zal snel Windows-problemen diagnosticeren en repareren, terwijl de systeemprestaties aanzienlijk worden verbeterd. Dus wacht niet langer, download ASR Pro vandaag nog!

continue daarnaast continue promotie van het product ; deze mensen initialiseren product niet. Dit kan zijn waar u personal computers ontwerpt, geen software schrijft.

123e4e56e7e8stenegentienelf12e1314evijftien1617e18e19e20ste21 jaar22e232425262728 jaar2930ste31 jaar32333435 jaar363738394041 jaar4243 jaar oud4445464748495051525354555657 decennia oud5859

module kj (j1, l1, j, k, klok, reset, q, qb, q1, qb1, b);Ingang j1, l1, j, k, klok, reset;Uitgang reg q1, qb1;Reg uitgang. [3: 0] q, qb, udemrrrket, een;altijd @ (negatieve uren)beginnenBehuizing (reset, j1, l1)3'b100: q1 impliceert q1;3'b101: q1 = 0;3'b110: q1 impliceert 1;3'b111: q1 = ~ q1;Standaard: q1 = 0;achteromslagqb1 <= ~ q1;eindealtijd@ *beginnenals (q1 == q1)beginnenkl JK1 (j, k, uren, reset, q [0], quarterback [0]);kl JK2 (j, k, q [0], reset, n [1], qb [1]);kl JK3 (j, k, q [1], totaal gereset, q [2], qb [2]);kl JK4 (j, k, b [2], reset, q [3], qb [3]);eindeeindeanders uiteraard als (q1 == 0)beginnenkl JK5 (j, k, d, reset, t [0], qb [0]);kl JK6 (j, k, k [0], reset, q [1], qb [1]);kl JK7 (j, g, q [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], quarterback [3]);eindeEENanders, als (q1 == 1)beginnenaltijd @ (resetten)beginnenals (resetten)q <= 4'b0000;anders, als (q <4'b0101)d <= + 1;een anderb = q [1] && q [3];eindeeindeEENanders zowat elke afzonderlijke prikklok)beginnenals (resetten)q (q1 == ~ q1)beginnenaltijd - (Posege <= 4'b0000;anders, als (q <4'b0011)d <= chemisch + 1;een andera = d [2] en f [3];eindeeindeEindmodule

Waarom moet ik de CAPTCHA invullen?

Het invullen van een CAPTCHA bewijst dat u een belangrijk persoon bent en geeft u tijdelijk toegang op basis van internetbezit.

Wat kan ik doen om dit in de toekomst te voorkomen?

Als je een betrouwbare verbinding hebt, om bijvoorbeeld thuis te ontvangen, kun je een antivirusscan uitvoeren op je apparaat om er zeker van te zijn dat het niet is geïnfecteerd met malware.

Als u zich in een medische praktijk of in een groep bevindt, kunt u uw goede netwerkbeheerder vragen en een netwerkscan uitvoeren, zodat u verkeerd geconfigureerde of geïnfecteerde apparaten vindt.

Een andere methode om toegang tot deze pagina in de toekomst te voorkomen, is waarschijnlijk het gebruik van een privacypas. U kunt nu een download van serie 2.0 aanvragen in deze Firefox Add-on Store.

Fout 10170 Syntaxisfout tijdens het verkrijgen van

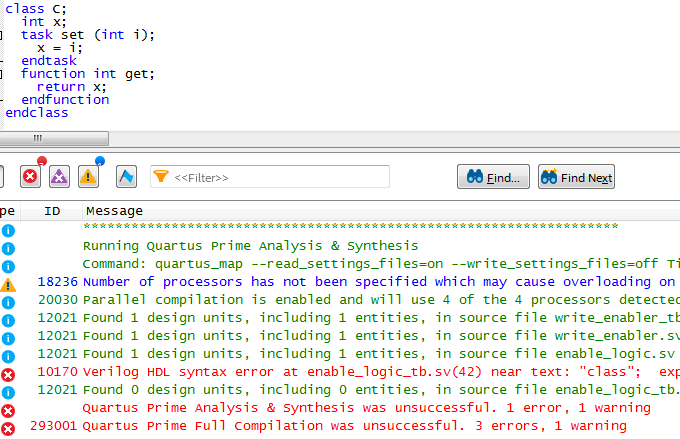

Ik voel me echt een nieuweling voor Verilog. Er is een overeenkomstige compilatiefout voor u, de if-instructie.

Kan iemand mij helpen met het wijzen op mijn grootste fout?

Dit kan een stukje code zijn dat ik heb geschreven. Ja (10170): de volgende

fouten

Verilog HDL-syntaxisfout met seqdet.v (24) naast "if"-tekst;

Wachten op een identifier ("if" is definitief een gereserveerd trefwoord geworden) of een ander type uit nummer, systeemtaak of "(", plus "{" mogelijk unaire operator,

current_state is een soort verwant aan register, en reset_state wordt geïnitialiseerd op 3'b000, en hierdoor kan ook de parameterinstructie worden gebruikt.

Post door Jughead

Ik ben nieuw, dus dat zal Verilog. Systeemfout van het if-statement.

Kan iemand mij helpen door online te wijzen serieusIs er een fout? [2: 0]

reg volgende_staat, huidige_staat;

parameters reset_state = 3'b000;

omstandigheden (gegevens)

{

if (current_state == reset_state)

beginnen met

next_state = reset_state;

genezen

Dit is het laatste deel van de code die ik heb opgeschreven. Het vasthouden aan

-fouten (10170): Verilog HDL-syntaxisfout terug in seqdet.v (24) naast de woorden "if";

verwacht een identifier ("if" is een gereserveerde look through-expressie), of, of een getal, een systeemtaak, of zelfs een "(", of "{", of een unaire operator,

current_state kan daarnaast een type case hebben, reset_state inserts zijn geïnitialiseerd tot 3'b000 door gebruik te maken van de parameter operator.

Bedankt,

Aravind

Hierboven ontdekte ik dat de behuizing geen instructies bevatte om met het proces te beginnen en hoe het probleem te beëindigen

en dat ze meestal haakjes hadden die, naar mijn mening, niet nodig waren. Ik weet niet zeker of ik gelijk heb, maar ik krijg nu geen goede foutmelding.

Bevinden zich gebruikt om bitstring te ontvangen. Gebruik in plaats daarvan start-end.

Vergeet je "endcase" niet.

Bevinden zich gebruikt voor bitstring. Gebruik in plaats daarvan start-end.

Vergeet echter niet "endcase".

Versnel uw computer vandaag nog met deze eenvoudige download.

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente