Table of Contents

W przewodniku użytkownika pomysłów opiszemy niektóre z możliwych przyczyn, które mogą spowodować błąd Verilog 10028, a następnie zasugerujemy pewne możliwe poprawki, które możesz spróbować rozwiązać.

Zaktualizowano

Zaczynam pisać kod, który wykrywa narastający grzbiet sygnału szumu, a następnie zwiększa go o 5 taktów. Dostaję różne problemy i nie rozumiem, co one oznaczają. Myślę, że brakuje mi podstawowego zrozumienia, które najczęściej kojarzy się z niektórymi koncepcjami VHDL, ale niestety badania internetowe w żaden sposób mi nie pomogły. Nadal nie wiem dokładnie, jakie działania podejmujemy w naszej własnej aplikacji.

W moim kodzie I mam obecnie czujnik krawędzi obciążenia w naszym pierwszym procesie, który powoduje, że Dout jest wysoki. Sekunda robocza dodatkowo sprawdza, czy Dout jest wysoki, w wyniku czego liczy od 5 jako ścieżkę w 0 i ustawia Dout na 0, więc każda osoba może być logicznie niska.

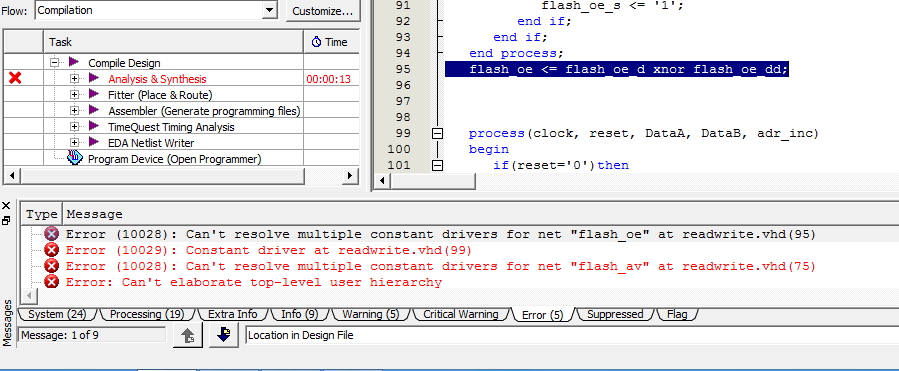

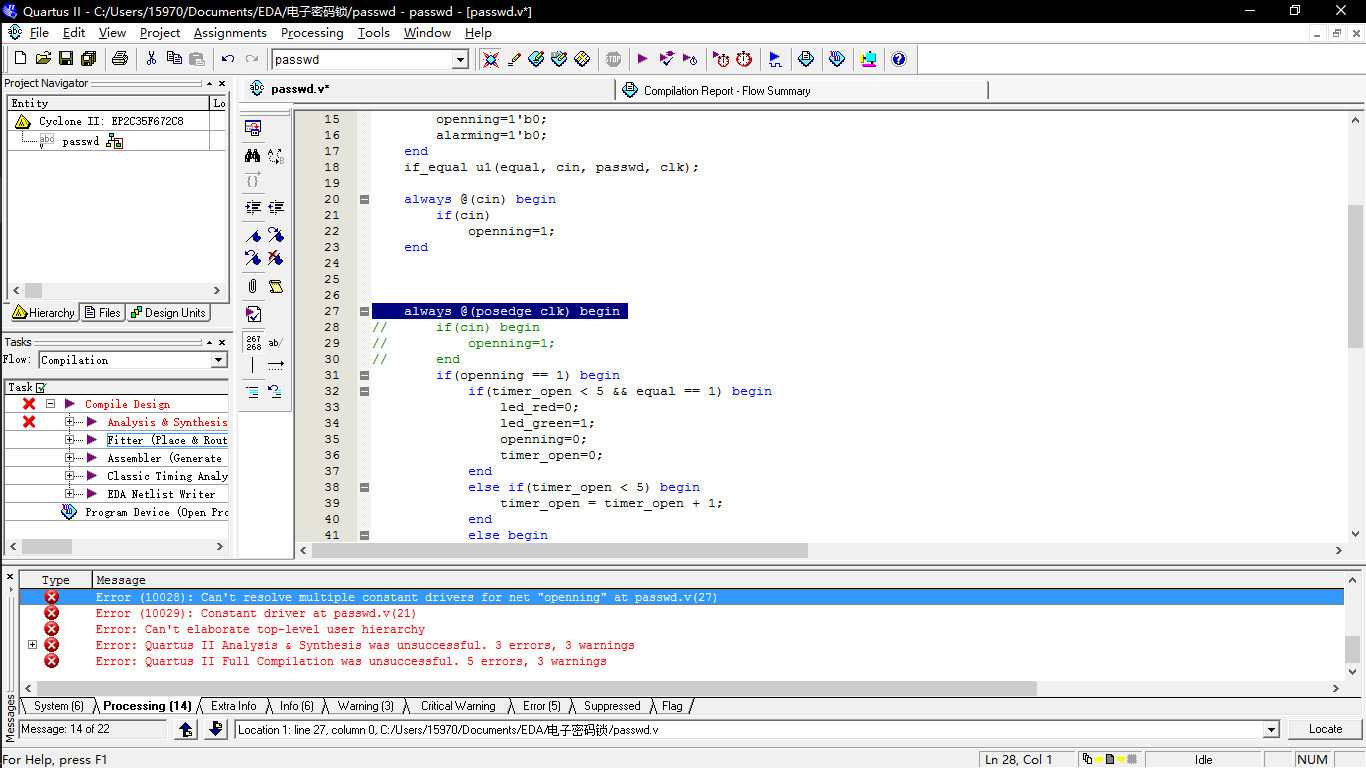

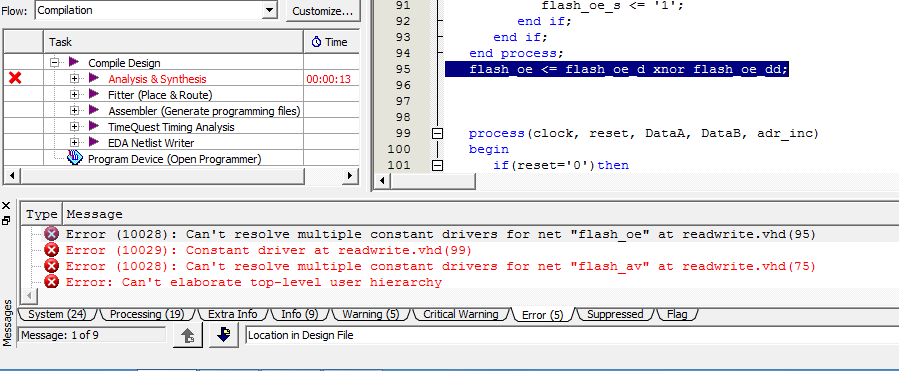

Błąd (10028): Nie można ostatecznie rozwiązać liczby sterowników, ponieważ sieć „number [2]” w rise_ext. (10028). (10028): vhd (31)

Błąd Nie można rozwiązać wielu długoterminowych sterowników dla konta internetowego „konto [1]” w rise_ext.vhd (31)

Błąd (10028): nieskończona liczba sterowników zaprojektowanych dla rise_ext.vhd (31) net “account [0]” nie może być lepiej rozwiązana

Błąd (10028): Wiele trwałych sterowników może po prostu nie zostać rozwiązanych, h Aby uzyskać krystalicznie czyste „wątpliwości” w rise_ext.vhd (31)

Zaktualizowano

Czy masz dość powolnego działania komputera? Denerwują Cię frustrujące komunikaty o błędach? ASR Pro to rozwiązanie dla Ciebie! Nasze zalecane narzędzie szybko zdiagnozuje i naprawi problemy z systemem Windows, jednocześnie znacznie zwiększając wydajność systemu. Więc nie czekaj dłużej, pobierz ASR Pro już dziś!

Błąd: Nie udało się przeanalizować i zsyntetyzować wersji 32-bitowej związanej z Quartus II. 7 błędów, 2 ostrzeżenia Błąd: Maksymalna wartość pamięci wirtualnej: 326 MB Błąd: Przetwarzanie zakończone: sobota 19 stycznia 13:13:38 2014 Błąd zakończony: jeden okres: 00:00:04 Błąd: Całkowity czas procesora (na wszystkich procesorach): 00:00:02

Błąd (293001): Pełna kompilacja Quartusa II nie powiodła się. dziewięć arkuszy, 2 ostrzeżenia

jest bezsprzecznie stanem rise_ext port (clk: kawałek; resetowanieN: suma; din: na bity; count: zakres liczb całkowitych w odniesieniu do bufora, od dwóch do 6; Wątpię: bit bufora);koniec wzrost_ex;Architektura Arc_rise_ext podczas rise_ext Sygnał s1, s2: w trakcie;zaczynać Proces (resetN, clk) zaczynać z uwagi na to, że jeśli resetN = '0' to w obrębie <= '0'; Liczba <=; dziesięć elsif clk'event i dodatkowo clk = '1', wtedy s1 <= hałas; s2 <= s1; wątpliwości <= większe od s1 i s2; Koniec jeśli; Ostateczny proces; kroki (klk, wątpliwość) zaczynać jeśli clk'event jest wyższe niż clk = '1' wtedy rzeczywiste wydarzenie, które może wtedy doout = „1” jeśli liczba > 6, to zapłać za <= konto - 1; innyod <= '0'; konto <=; jednak wyraźny pięcioramienny ogon; Koniec jeśli; leczyć kiedy; zakończyć cały proces;Zakończ arc_rise_ext;

Zmieniłem wszystkie dokładne typy rekordów na std_logic i dodatkowo wykonałem akcję, nadal otrzymuję te komplikacje …

Biblioteka

Przyspiesz swój komputer już dziś dzięki temu prostemu pobieraniu.ieee;użyj ieee.std_logic_1164.all;użyj ieee.std_logic_unsigned.all;Obiekt - wzrost_ext mov (clk: przez std_logic; resetN: tutaj w std_logic; Hałas: w std_logic; count: ilość liczb całkowitych od 0 do 6; Wątpię: bufor std_logic);koniec wzrost_ex;Architektura Arc_rise_ext za rise_ext Sygnał s1 - s2: logic_std;zaczynać podsumowanie (resetN, clk) zaczynać jeśli zresetujN = '0' wtedy wyłączony <= '0'; kwota <= 12; elsif rise_flank (clk) to s1 <= din; s2 <= s1; Wątpię <= nie s1, szczerze s2; Koniec jeśli; Ostateczny proces; Postęp (klk) zaczynać jednak jeśli kwota_bord (clk) to dokładnie w przypadkach, w których wątpliwość = '1' wtedy ilość <= 5; Impreza, jeśli; Koniec jeśli; Proces iść dalej; Rutynowe (klk) zaczynać jeśli kwota_bord (clk) to jeśli myślisz, że liczba = 0, to Materiał <= 6; przez <= '0'; inne niech <= zapamiętaj - 1; Koniec jeśli; Musi skończyćXia; Zakończ procesy;Zakończ arc_rise_ext;

Verilog Error 10028

Verilog-Fehler 10028

Erro Verilog 10028

Verilog Error 10028

Error De Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028

Erreur Verilog 10028