Table of Contents

Atualizado

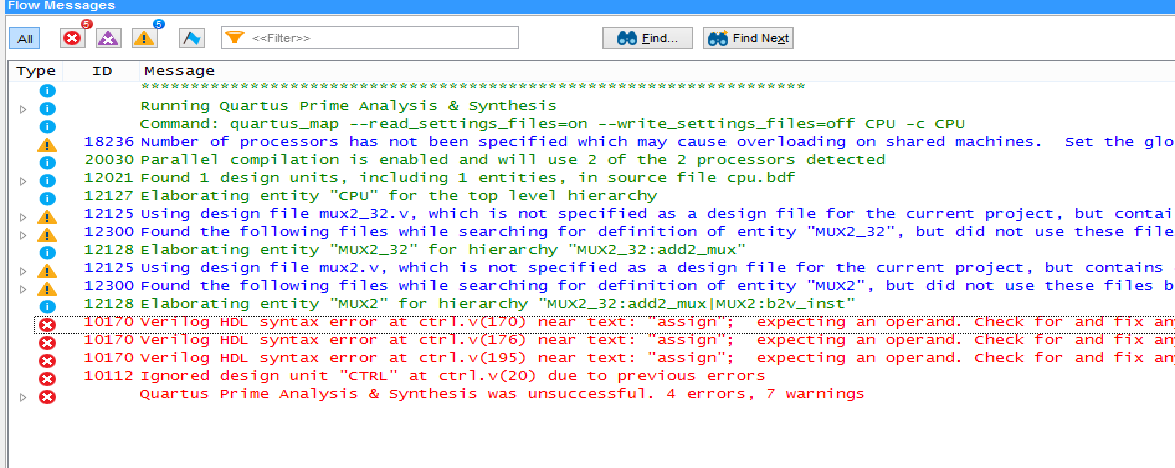

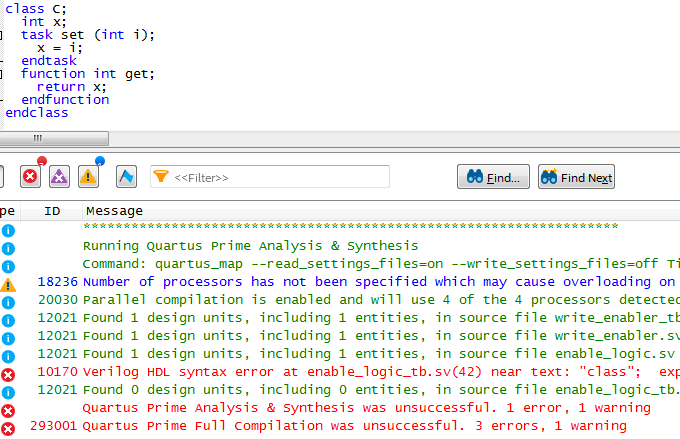

Nos últimos dias, alguns de nossos leitores informaram à empresa que encontraram o erro de sintaxe 10170 verilog hdl./ Erro (10170): Erro de formato Verilog HDL em .v (line_number) ao lado da nota de texto “,”; espera um operando. Devido ao seu problema com o software Quartus® II tipo 13.1 e superior, os proprietários podem receber o seguinte erro ao compilar um bom arquivo Verilog HDL convertido de um arquivo de unidade de bloco (.bdf).

O motivo do erro de formato é que você não pode simplesmente escrever:

items [7: 4] = 4'b0000;

Atribuir produto [7: 4] corresponde a 4'b0000;

Mas se você não usar o System Verilog (e seu estilo de codificação html antiquado presume que os clientes não usam), você descobrirá que um grande número < / p>

atribuir produto [7: 4] implica 4'b0000;

Além disso,

não compila porque o destino de alocar deve ser wire , não um reg . E se alguém alterar o produto para uma transferência completa, você verá que todas essas transações apresentam um erro:

suplemento de saúde = modelo 1; >> // mover para a direita geral e atribuir 0 à minha ordem elevadaProduto [7: 3] significa produto [7: 3] + multiplicando [4: 0]; // adicione 5 bits para que meu cônjuge e eu possamos controlar o relatório

product equivale à parte 1; >> // mover para a direita

realidade que uma pessoa não pode corresponder ao thread durar um grande bloco always (ou inicialmente ).

Você sempre parece fazer algum tipo de deslocamento e adicionar um bom multiplicador e / ou provavelmente deseja inicializar o produto no início do cálculo. (Supondo que você tenha uma sintaxe de grupo) linhas

(atribuir) plano de produto ou serviço [7: 4] 4'b0000;(Atribuir) = Produto [3: 0] = Multiplicador [3: 0];

Atualizado

Você está cansado de ver seu computador lento? Irritado com mensagens de erro frustrantes? ASR Pro é a solução para você! Nossa ferramenta recomendada diagnosticará e reparará rapidamente os problemas do Windows, aumentando drasticamente o desempenho do sistema. Então não espere mais, baixe o ASR Pro hoje mesmo!

Promoção contínua e contínua do produto ; eles não inicializam necessariamente o produto . É aqui que você precisa projetar computadores pessoais, não escrever software.

123ª4º56º7º8ºnovedezonze12º1314ºquinze16Dia 1718º19º20o21 anos22º232425262728 anos2930º31 anos32333435 anos363738394041 anos4243 anos4445464748495051525354555657 anos5859

módulo kj (j1, l1, j, e, clock, reset, q, qb, q1, qb1, b);Entrada j1, l1, j, k, relógio, redefinir;Saída reg q1, qb1;Saída de registro. [3: 0] q, qb, b, a;sempre - (horas negativas)começarCaso (redefinir, j1, l1)3'b100: q1 significa q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 implica ~ q1;Padrão: q1 = 0;Contracapaqb1 <=! q1;fimsempre@ *começarif (q1 == q1)começarkl JK1 (j, reino unido, horas, reset, q [0], qb [0]);kl JK2 (j, k, q [0], zerar, q [1], zagueiro [1]);kl JK3 (j, k, q [1], redefinir, e [2], qb [2]);kl JK4 (j, k, q [2], reformulação, q [3], qb [3]);fimfimcaso contrário, if (q1 == 0)começarkl JK5 (j, k, d, zerar, q [0], zagueiro [0]);kl JK6 (j, k, q [0], redefinir, k [1], qb [1]);kl JK7 (j, k, b [1], redefinir, q [2], qb [2]);kl JK8 (j, certo, q [2], redefinir, q [3], qb [3]);fimUMAcaso contrário, independentemente de (q1 == 1)começarsempre @ (redefinir)começarif (reset)q <= 4'b0000;caso contrário, se (q <4'b0101)d <= d + 1;outrob significa q [1] && q [3];fimfimUMAcaso contrário, todos os dias, relógio)começarif (reset)q (q1 == ~ q1)começarsempre @ (Posege <= 4'b0000;caso contrário, if (q <4'b0011)d <= d + 1;outroa é igual a d [2] e d [3];fimfimParte final

Por que preciso preencher o CAPTCHA?

O preenchimento de um CAPTCHA prova que você continua a ser uma pessoa importante e oferece acesso direto temporário com base na propriedade da Internet.

O que posso fazer para evitar isso no futuro?

Se você tiver uma conexão confiável, por exemplo em casa, poderá executar uma verificação de vírus no seu dispositivo para ter certeza de que ele não está apenas infectado por malware.

Se você estiver em um escritório ou em relação a um grupo, pode perguntar ao seu supervisor de rede e executar uma varredura de rede para localizar dispositivos mal configurados ou infectados.

Outra maneira de evitar o acesso a esta página no futuro é usar um Privacy Pass. Você pode solicitar o download da versão 2.0 nesta Loja de complementos do Firefox agora.

Erro 10170 Erro de sintaxe ao compilar

Simplesmente me sinto um novato em Verilog. Geralmente, há um erro de compilação correspondente para a pesquisa if.

Alguém pode me ajudar apontando para o meu maior erro?

Este é um artigo de código que escrevi. Sim (10170): a maioria dos seguintes

erros

Erro de formato Verilog HDL com seqdet.v (24) próximo ao texto "if";

Esperando por um identificador ("se" é definitivamente uma única palavra-chave reservada) ou qualquer tipo de número, tarefa de rede ou "(", mais "{" ou usuário unário,

current_state é uma espécie de registrador, assim como reset_state é inicializado em 3'b000, o que permite que esta instrução de parâmetro seja utilizada.

Postagem de Jughead

Sou novo na Verilog. Erro de sistema da instrução if.

Alguém pode me ajudar apontando para o que há de sério por engano? [2: 0]

reg next_state, current_state;

restrições reset_state = 3'b000;

case (data)

{

if (current_state == reset_state)

mexa-se

next_state = reset_state;

fim

Esta é a última parte da troca que escrevi. As seguintes correções de

(10170): Erro de sintaxe Verilog HDL em seqdet.v (24) após as palavras "if";

espera um grande identificador ("if" é uma expressão de pesquisa reservada), ou, possivelmente um número, uma tarefa do sistema, ou "(", e "{", ou um operador unário,

current_state pode ter um type case e reset_state inserts buy foram inicializados até 3'b000 usando a maior parte do operador de parâmetro.

Obrigado,

Aravind

Acima, descobri que o caso estava longe de ter instruções sobre como iniciar e como encerrar

e havia parênteses que, a meu ver, não são necessários. Não tenho certeza se estou bem, mas não estou recebendo um erro de agora em diante.

Estão localizados usado para bitstring. Em vez disso, use início e fim.

Não se esqueça do "endcase".

Estão localizados usado para bitstring. Em vez disso, use start-end, seu.

Não se esqueça, entretanto, de "endcase".

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente