Table of Contents

Обновлено

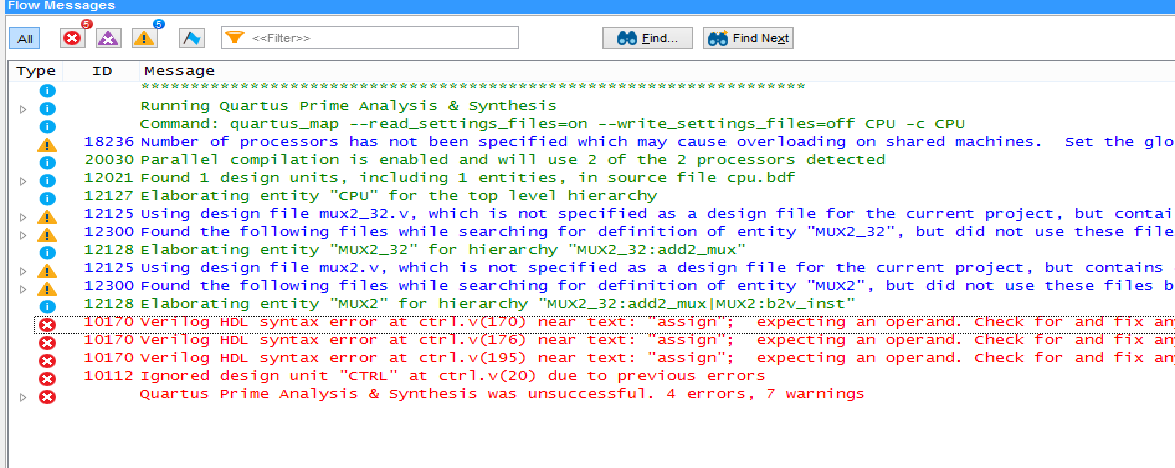

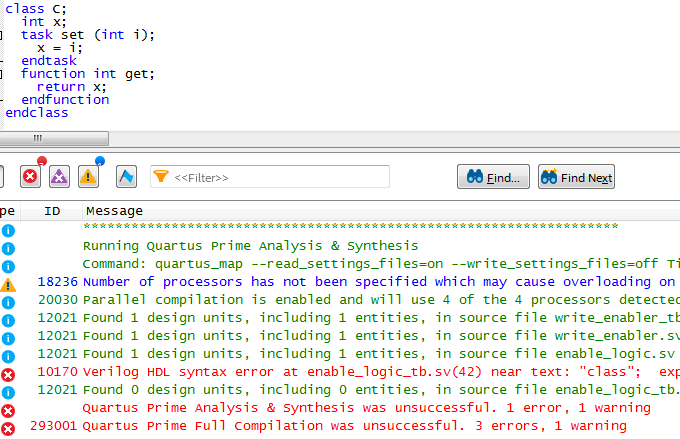

За последние несколько событий некоторые из наших читателей сообщили нам, где они столкнулись с синтаксической ошибкой 10170 Verilog липопротеина высокой плотности./ Ошибка (10170): синтаксическая ошибка Verilog HDL на всем протяжении .v (номер_строки) рядом с текстовым сообщением “,”; желает операнд. Из-за вашей проблемы с программным обеспечением Quartus® II типа 13.1 и выше, вы также можете получить следующую ошибку при компиляции файла Verilog HDL, преобразованного из файла данных блочного дизайна (.bdf).

Причина синтаксической ошибки в том, что вы не можете просто написать:

товар [7: 4] = 4'b0000;

Назначить машину [7: 4] соответствует 4'b0000;

Но если вы определенно не используете System Verilog (и ваше старомодное кодирование предполагает, что клиенты этого не делают), вы обнаружите, что все

присвоить продукт [7: 4] = 4'b0000;

Кроме того,

на самом деле не компилируется, потому что целью nominate должен быть wire , а не большинство недавний reg . И если вы переключите product на обычный перенос , вы обнаружите, что эти сделки дают вам ошибку:

продукт подразумевает модель 1; >> // переходим к точному и присваиваем 0 моему старшему разрядуПроизведение [7: 3] означает произведение [7: 3] + множимое [4: 0]; // добавляем 5 бит, чтобы мы могли контролировать отчет

product = часть 1; >> // двигаться вправо

потому что последний человек не может сопоставить thread в новом большом блоке always (или действительно ).

Кажется, вы всегда разрабатываете большинство видов смещения и добавляете множитель и / или вы, вероятно, хотите инициализировать тип product в начале, как при вычислении. (Предполагая, что вы группируете синтаксис) телефонные линии

(назначить) товар или услугу [7: 4] 4'b0000;(Назначить) = Продукт [3: 0] = Множитель [3: 0];

Обновлено

Вы устали от того, что ваш компьютер работает медленно? Раздражают разочаровывающие сообщения об ошибках? ASR Pro - это решение для вас! Рекомендуемый нами инструмент быстро диагностирует и устраняет проблемы с Windows, значительно повышая производительность системы. Так что не ждите больше, скачайте ASR Pro сегодня!

непрерывная и непрерывная реклама связана с продуктом ; они фактически не инициализируют product . Здесь вы создаете персональные компьютеры, а не пишете программное обеспечение.

123-й4-й56-е7-е8-едевять10одиннадцать12-е1314-епятнадцать1617-е18-е19-е20-е21 год22-е23242526 год2728 год2930-е31 год32333435 лет363738394041 год4243 года44 год45464748495051525354555657 лет5859

модуль kj (j1, l1, j, k, timepiece, reset, q, qb, q1, qb1, b);Вход j1, l1, j, k, часы, сброс;Выходной reg q1, qb1;Рег уйти. [3: 0] q, qb, b, a;всегда в (отрицательные часы)начинатьСлучай (сброс, j1, l1)3'b100: q1 = q1;3'b101: q1 равно 0;3'b110: q1 = 1;3'b111: q1 =! q1;По умолчанию: q1 = 0;Задняя обложкаqb1 <=! q1;конецвсегда@ *начинатьесли (q1 == q1)начинатьkl JK1 (j, k, рабочее время, сброс, q [0], qb [0]);kl JK2 (j, nited Kingdom, q [0], reset, q [1], qb [1]);kl JK3 (j, k, q [1], сброс, q [2], защитник [2]);kl JK4 (j, k, q [2], сбросить, e [3], qb [3]);конецконецв противном случае, если (q1 == 0)начинатьkl JK5 (j, k, d, сброс, q [0], защитник [0]);kl JK6 (j, k, q [0], сброс, королева [1], qb [1]);kl JK7 (j, k, q [1], сбросить в ноль, q [2], qb [2]);kl JK8 (j, k, b [2], сбросить, q [3], qb [3]);конецАв противном случае, будет ли (q1 == 1)начинатьвсегда @ (сбросить)начинатьесли (сбросить)q <= 4'b0000;в противном случае, если возможно (q <4'b0101)d <= d + 1;Другаяб = ш [1] && q [3];конецконецАиначе каждый раз часы)начинатьесли (сбросить)q (q1 == ~ q1)начинатьвсегда @ (Posege <= 4'b0000;в противном случае в пределах (q <4'b0011)d <= d + 1;Другаяa равно d [2] и d [3];конецконецФинальный модуль

Зачем нужно вводить CAPTCHA?

Заполнение CAPTCHA доказывает, что вы 1 важный человек, и дает вам временный доступ в Интернет.

Что я могу сделать, чтобы этого избежать в будущем?

Если у вашего сайта есть надежное соединение, например, в собственности, вы можете запустить сканирование на вирусы на всем своем устройстве, чтобы убедиться, что оно не заражено вредоносным ПО.

Если вы находитесь в офисе или в большой группе, вы можете попросить своего сетевого администратора, а также запустить сканирование сети, чтобы найти неправильно настроенные или возможно зараженные устройства.

Еще один способ предотвратить доступ к этой странице в будущем - это, скорее всего, использование Privacy Pass. Вы действительно запрашиваете загрузку версии 2.0 из Магазина надстроек Firefox прямо сейчас.

Ошибка 10170 Синтаксическая ошибка при компиляции

Я действительно новичок в Verilog. Имеется заслуживающая доверия соответствующая ошибка компиляции для оператора if.

Может ли кто-нибудь помочь мне, указав на самую большую ошибку?

Это часть кода, который я написал. Да (10170): сохранение с ошибками

Синтаксическая ошибка Verilog HDL из-за seqdet.v (24) рядом с текстом «если»;

Ожидание идентификатора ("if" определенно является запланированным ключевым словом) или числа любого типа, системной цели или "(", плюс "{" или унарного оператора,

current_state - это своего рода регистр, но reset_state инициализируется значением 3'b000, что позволяет использовать нашу собственную инструкцию параметра.

Опубликовать во времена Джагхеда

Я новичок в Verilog. Системная ошибка оператора if.

Может ли кто-нибудь поддержать меня, указав на серьезныеЕсть ли ошибка? [2: 0]

reg next_state, current_state;

выдает reset_state = 3'b000;

case (данные)

{

предположение (current_state == reset_state)

начало

next_state = reset_state;

конец

Это последняя часть кода, который я написал. Следующие

ошибки (10170): синтаксическая ошибка Verilog HDL в seqdet.v (24) далее в отношении слов «if»;

ожидает идентификатор ("if", без сомнения, зарезервированное поисковое выражение), или невероятное число, системная задача, или "(", или, может быть, "{", или унарный оператор,

current_state может предоставить регистр типа, а вставки reset_state недавно были инициализированы до 3'b000 с использованием параметраounter.

Спасибо,

Aravind

Выше я узнал, что в кейсе еще не было инструкций о том, как начать процесс, а также о том, как его завершить

и обычно, и у них были круглые скобки, которые, на мой взгляд, действительно были необходимы. Я не уверен, прав ли я, но, к сожалению, сейчас я не получаю сообщение об ошибке.

Расположены используется для битовой строки. Фактически используйте start-end.

Не забывайте о «заглушке».

Расположены используется для битовой строки. Вместо этого используйте start-end.

Не забывайте, однако, "endcase".

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente

г.