Table of Contents

Uppdaterad

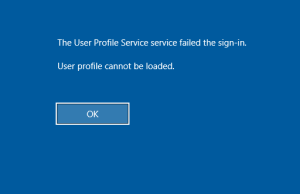

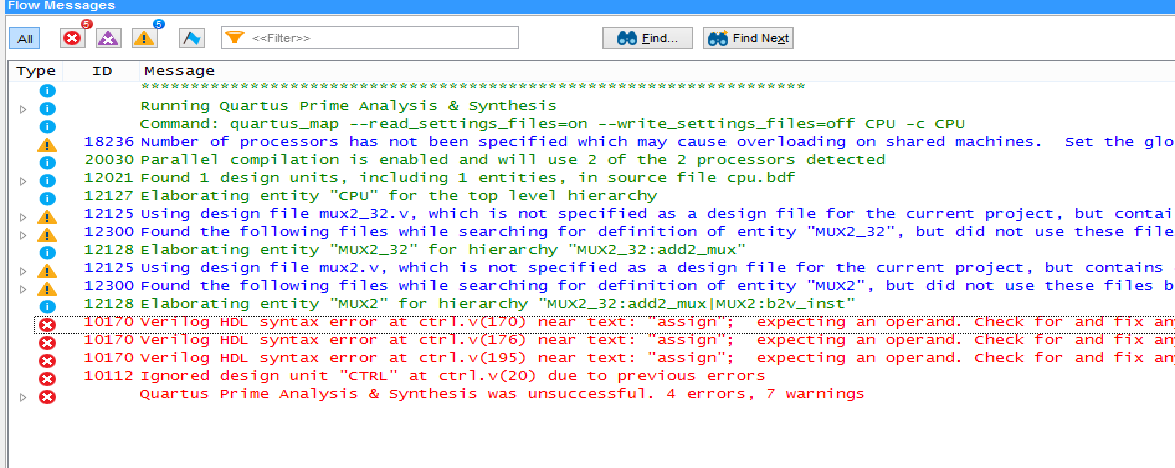

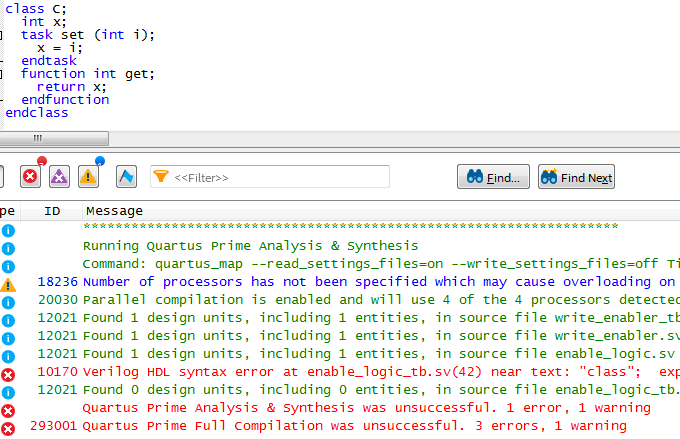

Under de senaste dagarna har några av våra läsare uppskattat informera oss om att de har stött på formatfel 10170 verilog hdl./ Fel (10170): Verilog HDL -syntaxfel i .v (radnummer) bredvid ett textmeddelande “,”; förväntar sig en operand. På grund av ditt alldeles egna problem med Quartus® II -programvarutyp 13.1 dessutom ovan kan du få följande fel om du kompilerar en Verilog HDL -fil konverterad från din egen blockdesignfil (.bdf).

Anledningen till det specifika syntaxfelet är att du inte bara kan publicera:

produkt [7: 4] = 4'b0000;

Tilldela produkt [7: 4] motsvarar med avseende på 4'b0000;

Men om du inte använder System Verilog (och din egen gammaldags kodningsstil förutsätter att klienter inte gör det), kommer du att söka efter att de flesta < /p>

tilldela produkt [7: 4] är lika med 4'b0000;

Också, <

kompileras inte eftersom målet som är länkat till tilldela bör vara rader , inte senaste reg . Och om du ändrar produkten för att hjälpa dig med en fullständig överföring ser du att dessa transaktioner ger dig ett fel:

product = modell 1; >> // fortsätt flytta till höger och tilldela 0 till flera andra högordrarProdukt [7: 3] betyder produkt [7: 3] + multiplicand [4: 0]; // lägg till 5 portioner så att vi kan styra rapporten

model = del 1; >> // gå till höger

eftersom en person inte kan matcha plats i ett stort alltid (eller initialt ) block.

Du känner alltid för att utforma någon form av förskjutning och öka a -multiplikatorn och / eller du skulle förmodligen verkligen vilja initiera -produkten < / kod> genom att gå till början av beräkningen. (Antar att du grupperar syntax) rader

(tilldela) produkt alternativt service [7: 4] 4'b0000;(Tilldela) = Produkt [3: 0] betyder multiplikator [3: 0];

Uppdaterad

Är du trött på att din dator går långsamt? Irriterad av frustrerande felmeddelanden? ASR Pro är lösningen för dig! Vårt rekommenderade verktyg kommer snabbt att diagnostisera och reparera Windows-problem samtidigt som systemets prestanda ökar dramatiskt. Så vänta inte längre, ladda ner ASR Pro idag!

kontinuerlig eller kontinuerlig marknadsföring av produkten ; dessa människor initierar inte produkt . Det är i allmänhet här du designar persondatorer, inte skrivverktyg.

123: e4: e56: e7: e8: eniotioelva12: e1314: efemton1617: e18: e19: e20: e21 år22: a232425262728 år2930: e31 år32333435 år363738394041 år4243 år gammal4445464748495051525354555657 lång gammal5859

modul kj (j1, l1, j, k, klocka, reset, q, qb, q1, qb1, b);Ingång j1, l1, j, k, klocka, återställning;Utmatningsreg q1, qb1;Reg exit. [3: 0] q, qb, d, a;alltid @ (negativa timmar)BörjaFodral (återställ, j1, l1)3'b100: q1 är lika med q1;3'b101: q1 = 0;3'b110: q1 motsvarar 1;3'b111: q1 = ~ q1;Standard: q1 = 0;Bakstycketqb1 <= ~ q1;slutetalltid@ *Börjaom (q1 == q1)Börjakl JK1 (j, k, timmar, återställning, q [0], quarterback [0]);kl JK2 (j, k, q [0], reset, queen [1], qb [1]);kl JK3 (j, k, q [1], återställ till noll, q [2], qb [2]);kl JK4 (j, k, e [2], reset, q [3], qb [3]);slutetslutetannars, om (q1 == 0)Börjakl JK5 (j, k, d, reset, e [0], qb [0]);kl JK6 (j, k, fråga [0], återställning, q [1], qb [1]);kl JK7 (j, e, q [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], quarterback [3]);slutetAannars, om (q1 == 1)Börjaalltid @ (återställ)Börjaom (återställ)q <= 4'b0000;annars, om (q <4'b0101)d <= t + 1;annanb = q [1] && q [3];slutetslutetAannars och även klocka)Börjaom (återställ)q (q1 == ~ q1)Börjaalltid på (Posege <= 4'b0000;annars, om (q <4'b0011)d <= ve hade + 1;annana = d [2] och k [3];slutetslutetSlutmodul

Varför behöver jag fylla i CAPTCHA?

Att slutföra en CAPTCHA bevisar att du är en viktig person och ger varje person tillfällig åtkomst baserat på internetägande.

Vad kan jag göra för att undvika detta i framtiden?

Om du har en pålitlig anslutning, för att ha ett exempel hemma, kan du köra en antitrojanskanning på din enhet för att se till att den inte är infekterad med skadlig kod.

Om du är i en byrå eller i en grupp kan du fråga den bästa nätverksadministratören och köra en nätverksskanning för att äntligen hitta felkonfigurerade eller infekterade enheter.

Ett annat val för att förhindra åtkomst till den här sidan i en specifik framtid är att detta troligen kommer att använda ett Privacy Pass. Du kan begära en nedladdning av formulär 2.0 från denna Firefox Add-on Store nu.

Fel 10170 Syntaxfel vid databasering

Jag känner mig verkligen som en nybörjare på Verilog. Det finns ett motsvarande kompileringsfel för alla if -satsen.

Kan någon hjälpa mig och även påpeka mitt största misstag?

Detta är utan tvekan en kodbit jag har skrivit. Ja (10170): följande

-fel

Verilog HDL -syntaxfel med seqdet.v (24) nästa på väg till "if" -text;

Väntar på en identifierare ("om" förmodligen definitivt är ett reserverat sökord) eller någon typ som är relaterad till nummer, systemuppgift eller "(", plus "{" eller annars unary operator,

current_state är ett slag som kommer från alla register och reset_state initialiseras till 3'b000, vilken typ av parametrar kan användas.

Inlägg av Jughead

Jag är ny för Verilog. Systemfel i if -satsen.

Kan någon hjälpa mig genom att påpeka såväl som seriöst Finns det ett misstag? [2: 0]

reg next_state, current_state;

parametrar reset_state = 3'b000;

händelse (data)

{

if (current_state == reset_state)

börja

next_state = reset_state;

wind

Det här är den sista delen av all kod jag skrev ner. Efterfel (10170): Verilog HDL -syntaxfel hela vägen genom seqdet.v (24) bredvid orden "if";

väntar sig en identifierare ("om" är ett reserverat undersökningsuttryck), eller, eller ett nummer, en systemuppgift, tillsammans med "(" eller "{", eller en unary operator,

current_state kan ha ett typfall tillsammans med reset_state -insatser har initierats upp till 3'b000 med hjälp av parameteroperatören.

Tack, Aravind

Ovan fick jag reda på att omständigheterna inte hade några instruktioner om hur processen skulle påbörjas och hur saker skulle avslutas

och vanligtvis hade de parenteser som enligt min individuella uppfattning inte behövdes. Jag är inte säker medan jag har rätt, men jag får inget fel just nu.

Ligger används eftersom bitsträng. Använd start-end istället.

Glöm inte vårt eget "endcase".

Ligger används för bitsträng. Använd start-end istället.

Glöm dock inte "endcase".

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente