Table of Contents

Updated

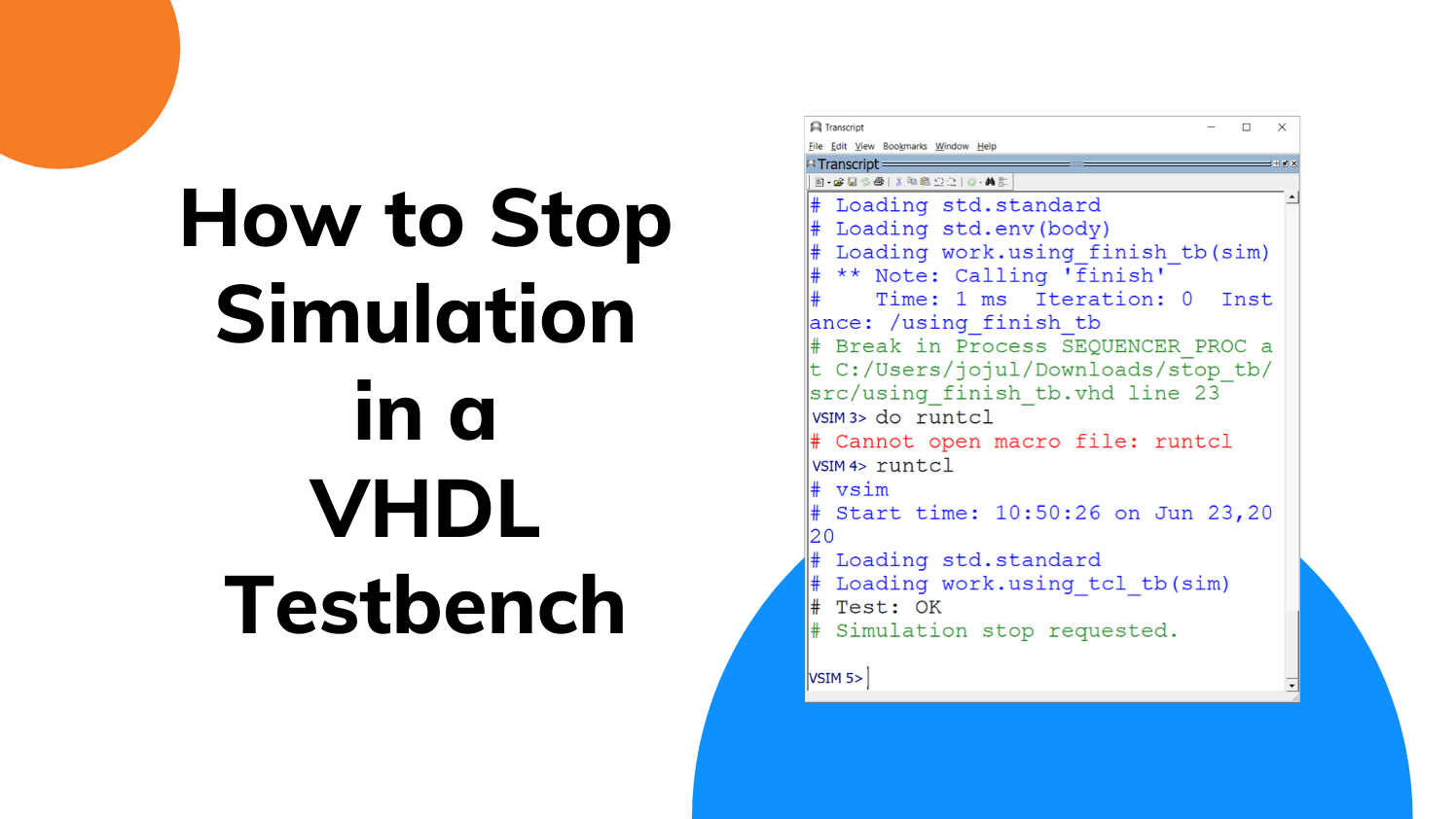

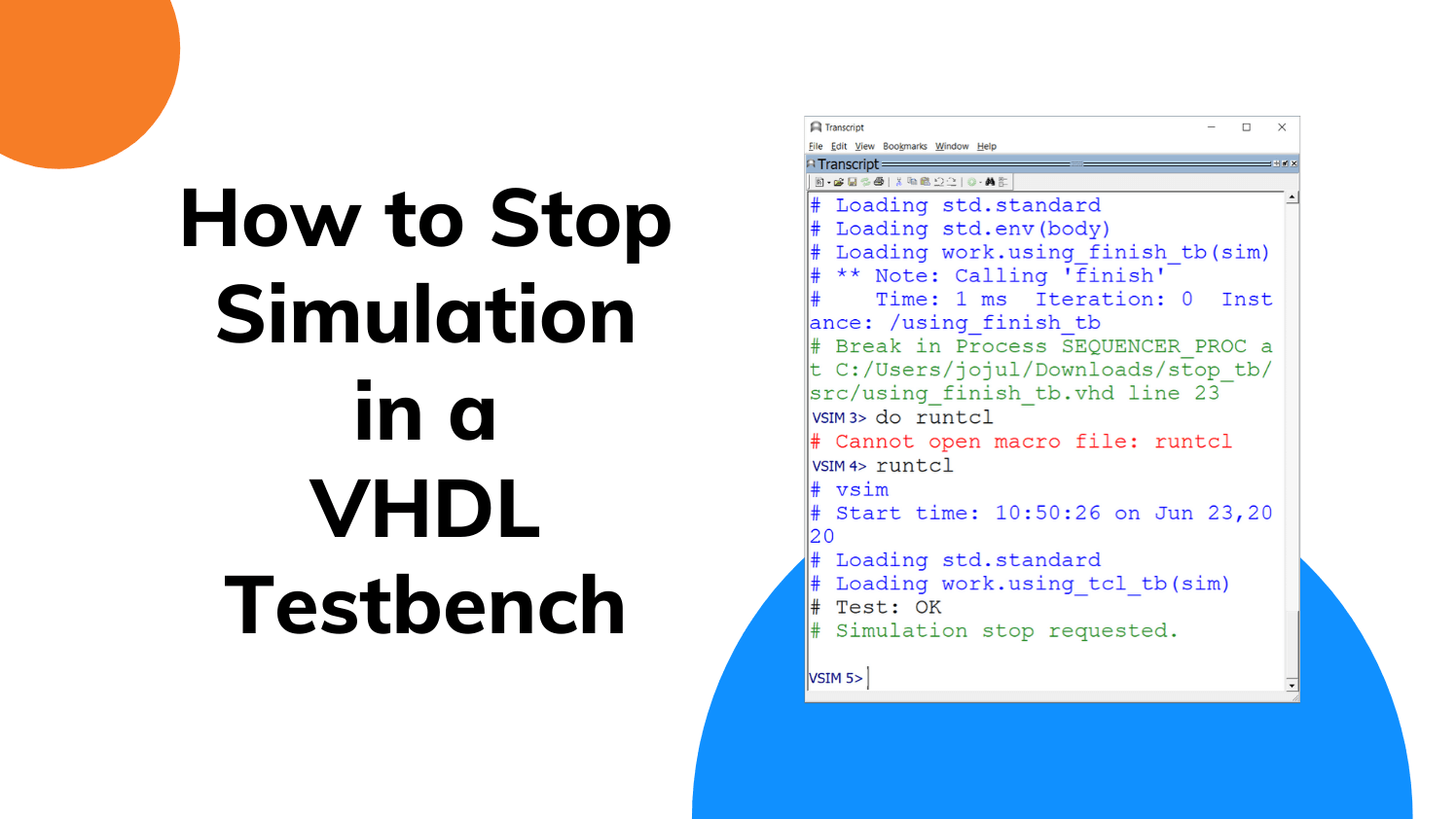

Recently, some of our users reported that they encountered error vsim-3817.

This error occurs in ModelSim® for VHDL projects. (Similar errors can occur in other EDA modeling tools.)

When the Quartus® II software generates a gateway-level VHDL netlist for third-party simulation tools (* .vho) for a project that allows any on-chip troubleshooting using the primary JTAG port (e.g. SignalTap®) may contain ® II logic analyzer or SOPC Builder JTAG UART) netlist contains the following JTAG ports:

- altera_reserved_tms

- altera_reserved_tck

- altera_reserved_tdi

- altera_reserved_ntrst

- altera_reserved_tdo

The error occurs when you simulate a top-level module using a test bench in a third-party modeling tool, if you do not specify these JTAG ports when declaring and instantiating top-level components.

To avoid this issue, specify JTAG ports in your component declaration and therefore instantiate your own test bench as shown below:

COMPONENT

You can set this altera_reserved * -pinastre to the logic 0 level of the new testbed as follows, since you will not send any data to these ports during simulation.

(Yes, I understand that there is an easier way, yes, my teacher asks me about the long journey.)The implementation is the code for my little adder / subtractor.

Library

ieee;use ieee.std_logic_1164.all;The entity is FA1Bit. port (x, y, Cin: to std_logic; op: only in std_logic; S, Cout: out std_logic);End of FA1Bit;Architecture - FA1Bit_arch by FA1Bitbegin Methods: PROCESS (op, x, y, Cin) begin if op means '0' then - when we add the bits; just like Cin = '0' then if x = y, then S <= '0'; if (x= '1' and a y = '1'), then Cost <= '1'; more details - if x = 0 and gym = 0; Stream <= '0'; End if; else - if x does not match y; S <= '1'; Stream <= '0'; End if; else - if Cin is 1, then; regardless of whether x = y, then S <= '1'; if (x = '1' and y just = '1') then Cost <= '1'; else - real event when x = 0 and y is 0; Stream <= '0'; End if; else - if x is not equal to y; S <= '0'; Cost <= '1'; liquidate when; End if; new - if you subtract bits (op is 1); if Cin = '0' then if x = Fahrenheit then Stream <= '0'; S <= '0'; elsif (x = '1' and y = '0') then Stream <= '0'; S <= '1'; otherwise, in the case when x is not equal to y; S <= '1'; Cost <= '1'; End if; else - assuming that then Cin = 1; if x = y, then Cost <= '1'; S <= '1'; elsif (x = '1' plus y = '0') then Stream <= '0'; S <= '0'; else - if x is not equal to y; S <= '0'; Cost <= '1'; End if; End, If; End if; Completion of the PROCESS;End FA1Bit_arch;

I am now using this element in my 4 bit adder / subtractor in this key fact code:

IEEE Library

;use IEEE.std_logic_1164.all;The entity is FA4Bit.Harbor (X: inside STD_LOGIC_VECTOR (3 to 0);Y: in STD_LOGIC_VECTOR (3 to 0);C0: in STD_LOGIC;S: from STD_LOGIC_VECTOR (from 3 to 0);C4: from STD_LOGIC;OP1: in STD_LOGIC_VECTOR (3 DOWN 0));End of FA4Bit;Architecture - FA4Bit_arch by FA4BitFA1bit componentport (X: in STD_LOGIC; Y: in STD_LOGIC; CIN: in: std_logic;if on STD_LOGIC; COST: from STD_LOGIC;OPA: in STD_LOGIC);Final component;Signal C: std_logic_vector (1 to 3);beginU1: city plan FA1bit (X => X (0), Y => Y (0), CIN => C0, SI => S (0), COUT => C (1), OPA => OP1 (0) );U2: FA1bit port manual (X => X (1), Y => Y (1), CIN => C (1), SI => S (1), COUT => C (2), OPA => OP1 ) (1));U3: FA1bit Portmap (X => X (2), Y => Y (2), CIN => C (2), SI => S (2), COUT => C (3), OPA => OP1 ( 2));U4: FA1bit Portmap (X => X (3), Y => Y (3), CIN => C (3), SI => S (3), COUT => C4, OPA => OP1 (3)) ;End of FA4Bit_arch;

Library

Updated

Are you tired of your computer running slow? Annoyed by frustrating error messages? ASR Pro is the solution for you! Our recommended tool will quickly diagnose and repair Windows issues while dramatically increasing system performance. So don't wait any longer, download ASR Pro today!

ieee;use ieee.std_logic_1164.all;Entity - FA4Bit_tbFinish;Architectural arch FA4Bit_tbFA4Bit component Port (X1: in std_logic_vector (3 0); before Y: in std_logic_vector (3 0); before C0: via std_logic; S: with std_logic_vector (3 0); before C4: out std_logic; OP1: in std_logic_vector (3 to 0));Final component;Signal X dfor std_logic_vector (3 to 0): = "0000";Signal Y (empty) std_logic_vector (3 to 0): = "0000";Report C0! ! ! std_logic: = '0';opa signal: std_logic_vector (3 to 0): equal (other => '0');S signal: std_logic_vector (3 0); signal down C4: std_logic;begin Test item: FA4Bit Port tour (X1 => X, Y => Y, C0 => C0, S => S, C4 => C4, OP1 => opa);X <= not X every five ns;Y <= not Y in eight ns;opa <= not opa after trying to find ns;End of arc;

# ** Fatal: (vsim-3817) Port "X" for object "fa4bit" is not half created.# Time: 7 ns Iteration: 0 Instance: / fa4bit_tb / UUT file: C: / Users / Omar / Desktop / 320 PROJECT 3ANJAD HAL MARRA / FA4Bit.vhd Line: 5#FATAL ERROR loading design# Error while starting design

Speed up your computer today with this simple download.

Устранение ошибки Vsim-3817

Errore Di Risoluzione Dei Problemi Vsim-3817

Probleemoplossing Fout Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L'erreur Vsim-3817

오류 Vsim-3817 문제 해결

Solución De Problemas De Error Vsim-3817

Fehlerbehandlung Vsim-3817

Felsökning Av Fel Vsim-3817

Solução De Problemas De Erro Vsim-3817