Table of Contents

Bijgewerkt

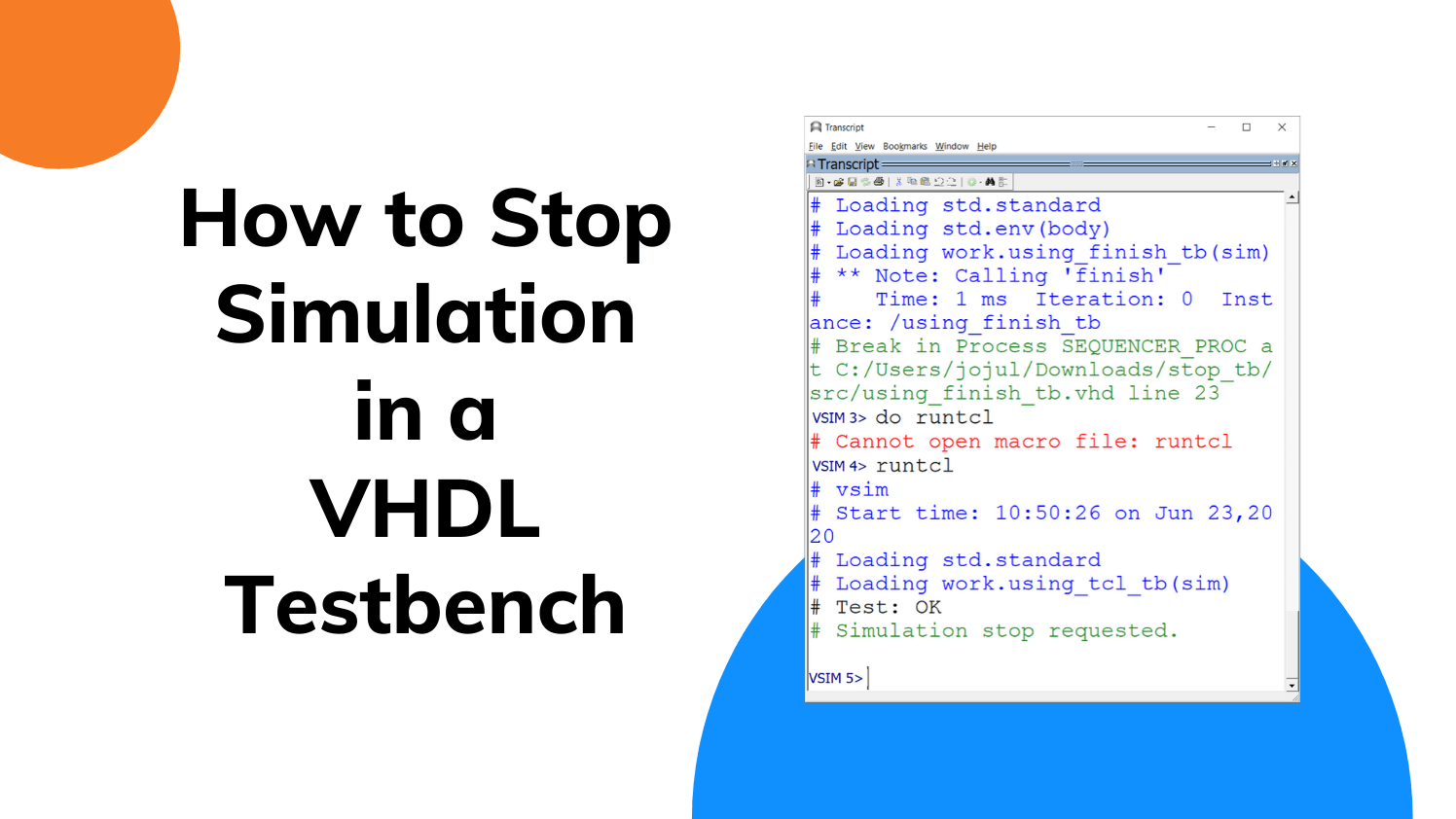

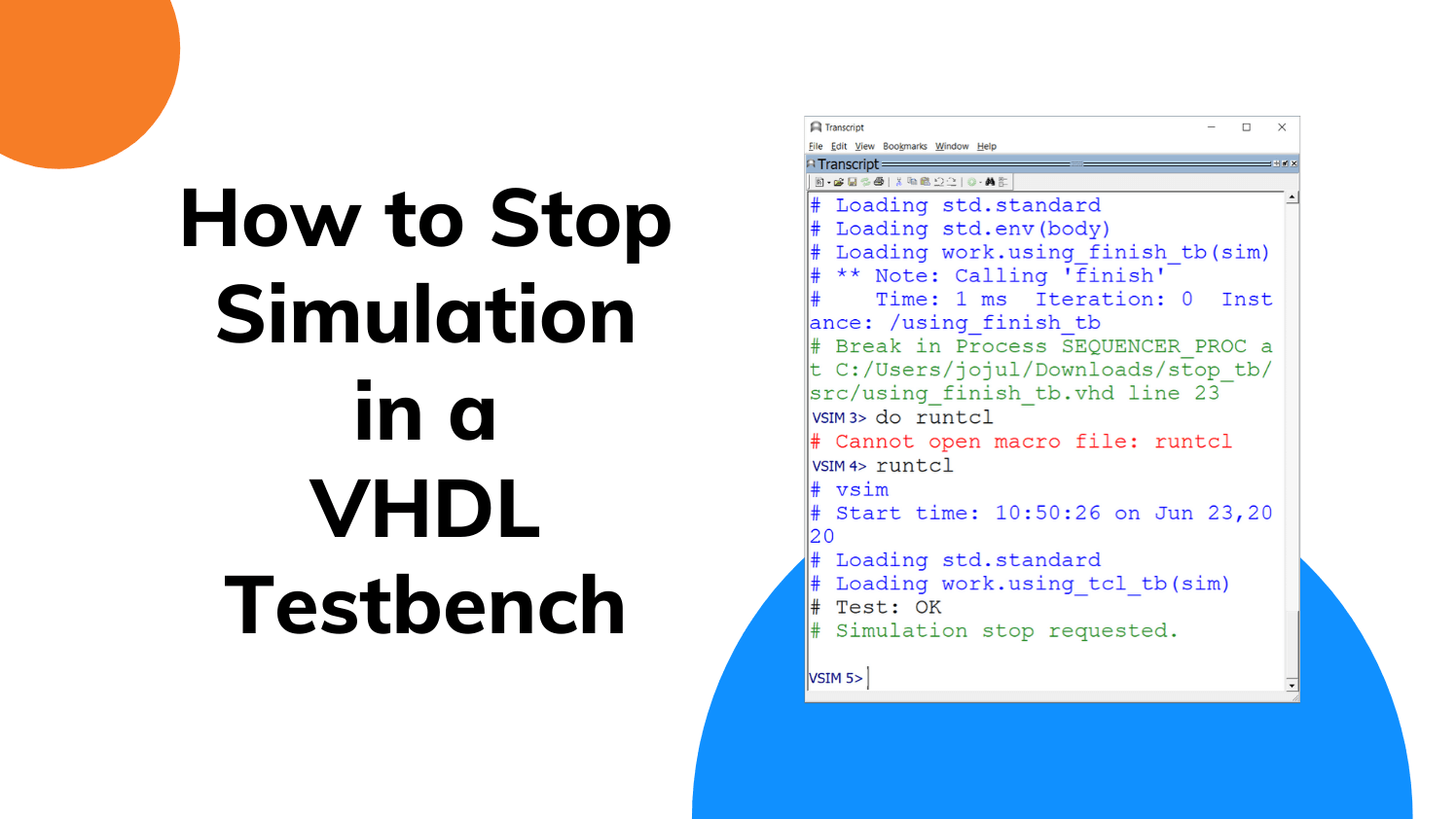

Onlangs meldden enkele van onze spelers dat ze de fout vsim-3817 tegenkwamen.

Deze fout treedt op in ModelSim® voor VHDL-mogelijkheden. (Vergelijkbare fouten kunnen voorkomen in andere EDA keuzehulpmiddelen.)

Wanneer de Quartus® II-software een VHDL-netlijst op gatewayniveau genereert naar simulatietools van derden (* .vho) voor een project, is het feit dat elke on-chip probleemoplossing met behulp van de primaire JTAG-poort (bijv. SignalTap®) kan ® II reasoning analyzer of SOPC Builder JTAG UART bevatten) netlist bevat de volgende JTAG-poorten:

- altera_reserved_tms

- altera_reserved_tck

- altera_reserved_tdi

- altera_reserved_ntrst

- altera_reserved_tdo

De fout treedt op in het geval dat u een module op het hoogste niveau simuleert met behulp van een proefbank in een modelleertool van derden, als iemand deze JTAG-poorten niet specificeert wanneer expressie en het instantiëren van componenten op het hoogste niveau.

Om bepaalde problemen te voorkomen, specificeert u JTAG-poorten in uw componentenonderzoek en maakt u daarom uw eigen testbank zoals hieronder weergegeven:

COMPONENT

PORT (

altera_reserved_tms. IN std_logic;

altera_reserved_tck: IN std_logic; altera_reserved_tdi: while std_logic;

altera_reserved_ntrst: In std_logic Altera_reserved

U kunt deze altera_reserved ( spatie ) -pinastre als volgt instellen op het logische 0-niveau van het betere testbed, aangezien u tijdens de simulatie geen gegevens naar deze poorten doorstuurt .

PORT MAP (

=> altera_reserved_tms '0',

altera_reserved_tck = > '0',

altera_reserved_tdi => '0',

Altera_reserved_ntrst => '0',

altera_reserved_tdoa_reserved_t => tdo, A

AAAAA ...

);

(Ja, ik begrijp dat er een makkelijkere manier is, ja, mijn leraar vraagt me om de lange reis.)De implementatie is de code om mijn kleine opteller / aftrekker te ontvangen.

Bibliotheek

ieee;gebruik ieee.std_logic_1164.all;De entiteit is FA1Bit. transport (x, y, Cin: naar std_logic; op: nauwelijks in std_logic; S, Cout: uit std_logic);Einde van FA1Bit;Architectuur - FA1Bit_arch door FA1Bitbeginnen Methoden: PROCES (op, x, y, Cin) beginnen if op assets '0' dan - wanneer we de bits toevoegen; wil gewoon Cin = '0' dan en als x = y, dan S <= '0'; if (x= '1' evenals de a y = '1'), dan Kosten <= '1'; meer details - if times = 0 en gym = 0; Stroom <= '0'; Stop als; als je dat niet doet - als x niet aansluit bij y; S <= '1'; Stroom <= '0'; Stop als; anders dan jij - als Cin 1 is, dan; ongeacht of x = sportschool, dan S <= '1'; als (x = '1' en b gewoon = '1') dan Kosten <= '1'; anders - echte gebeurtenis wanneer x 0 betekent en y 0 is; Stroom <= '0'; Stop als; soortgelijk - als x niet gelijk is aan y; S <= '0'; Kosten <= '1'; verkopen wanneer; Stop als; nieuw - ervan uitgaande dat je bits aftrekt (op is 1); als Cin '0' impliceert, dan als x Fahrenheit betekent, dan Stroom <= '0'; S <= '0'; elsif (x = '1' en y betekent '0') dan Stroom <= '0'; S <= '1'; anders, in het geval dat x niet gelijk is aan y; S <= '1'; Kosten <= '1'; Stop als; anders - aangenomen waarin dan Cin = 1; eenmaal x = y, dan Kosten <= '1'; S <= '1'; elsif (x = '1' moet y = '0') dan Stroom <= '0'; S <= '0'; anders - als x niet gelijk moet zijn aan y; S <= '0'; Kosten <= '1'; Stop als; Stop als; Stop als; Afronding van het PROCES;Einde FA1Bit_arch;

Ik gebruik dit element momenteel in mijn 4 tad opteller / aftrekker in deze belangrijke feitencode:

IEEE Bibliotheek

;gebruik IEEE.std_logic_1164.all;De entiteit is FA4Bit.Haven (X: binnen STD_LOGIC_VECTOR (3 tot 0);Y: in STD_LOGIC_VECTOR (3 tot 0);C0: in STD_LOGIC;S: van STD_LOGIC_VECTOR (van 3 tot 0);C4: van STD_LOGIC;OP1: in STD_LOGIC_VECTOR (3 DOWN 0));Einde van FA4Bit;Architectuur - FA4Bit_arch door FA4BitFA1bit-componentpoort (X: in STD_LOGIC; Y: in STD_LOGIC; CIN: in: std_logic;indien op STD_LOGIC; KOSTEN: van STD_LOGIC;OPA: in STD_LOGIC);Laatste onderdeel;Signaal C: std_logic_vector (1 tot 3);beginnenU1: stadsconfiguratie FA1bit (X => X (0), Y => Y (0), CIN => C0, SI => S (0), COUT => C (1), OPA => OP1 (0 ) );U2: FA1bit poort handmatig (X => X (1), Y => Y (1), CIN => C (1), SI => S (1), COUT => C (2), OPA => OP1 ) (1));U3: FA1bit Portmap (X => X (2), Y => Y (2), CIN => C (2), SI => S (2), COUT => C (3), OPA => OP1 ( 2));U4: FA1bit Portmap (X => X (3), Y => Y (3), CIN => C (3), SI => S (3), COUT => C4, OPA => OP1 (3)) ;Einde van FA4Bit_arch;

Bibliotheek

Bijgewerkt

Bent u het beu dat uw computer traag werkt? Geërgerd door frustrerende foutmeldingen? ASR Pro is de oplossing voor jou! Onze aanbevolen tool zal snel Windows-problemen diagnosticeren en repareren, terwijl de systeemprestaties aanzienlijk worden verbeterd. Dus wacht niet langer, download ASR Pro vandaag nog!

ieee;gebruik ieee.std_logic_1164.all;Entiteit - FA4Bit_tbFinish;Architecturale boog FA4Bit_tbFA4Bit-component Poort (X1: in std_logic_vector (3 0); voor Y: in std_logic_vector (3 0); voor C0: via std_logic; S: voor std_logic_vector (3 0); voor C4: uit std_logic; OP1: in std_logic_vector (3 tot 0));Laatste onderdeel;Signaal X dfor std_logic_vector (3 tot 0): betekent "0000";Signaal Y (leeg) std_logic_vector (3 tot 0): komt overeen met "0000";Meld C0! ! ! std_logic: = '0';opa signaal: std_logic_vector (3 tot 0): gelijk (overig => '0');S-stimulus: std_logic_vector (3 0); signaal omlaag C4: std_logic;beginnen Testitem: FA4Bit Havenrondvaart (X1 => X, Y => Y, C0 => C0, S => S, C4 => C4, OP1 => opa);X <= niet X vijf ns;Y <= niet Y in acties ns;opa <= niet opa na het proberen te realiseren van ns;Einde van boog;

# ** Fataal: (vsim-3817) Poort "X" voor object "fa4bit" is niet voor 60% gemaakt.# Tijd: 7 ns Iteratie: 0 Instantie: voor elk fa4bit_tb / UUT-bestand: C: / Gebruikers of Omar / Desktop / 320 PROJECT 3ANJAD HAL MARRA / FA4Bit.vhd Regel: 5#FATAL ERROR lancering ontwerp# Fout bij het starten van het ontwerp

Versnel uw computer vandaag nog met deze eenvoudige download.

Troubleshooting Error Vsim-3817

Устранение ошибки Vsim-3817

Errore Di Risoluzione Dei Problemi Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L'erreur Vsim-3817

오류 Vsim-3817 문제 해결

Solución De Problemas De Error Vsim-3817

Fehlerbehandlung Vsim-3817

Felsökning Av Fel Vsim-3817

Solução De Problemas De Erro Vsim-3817