Table of Contents

Actualizado

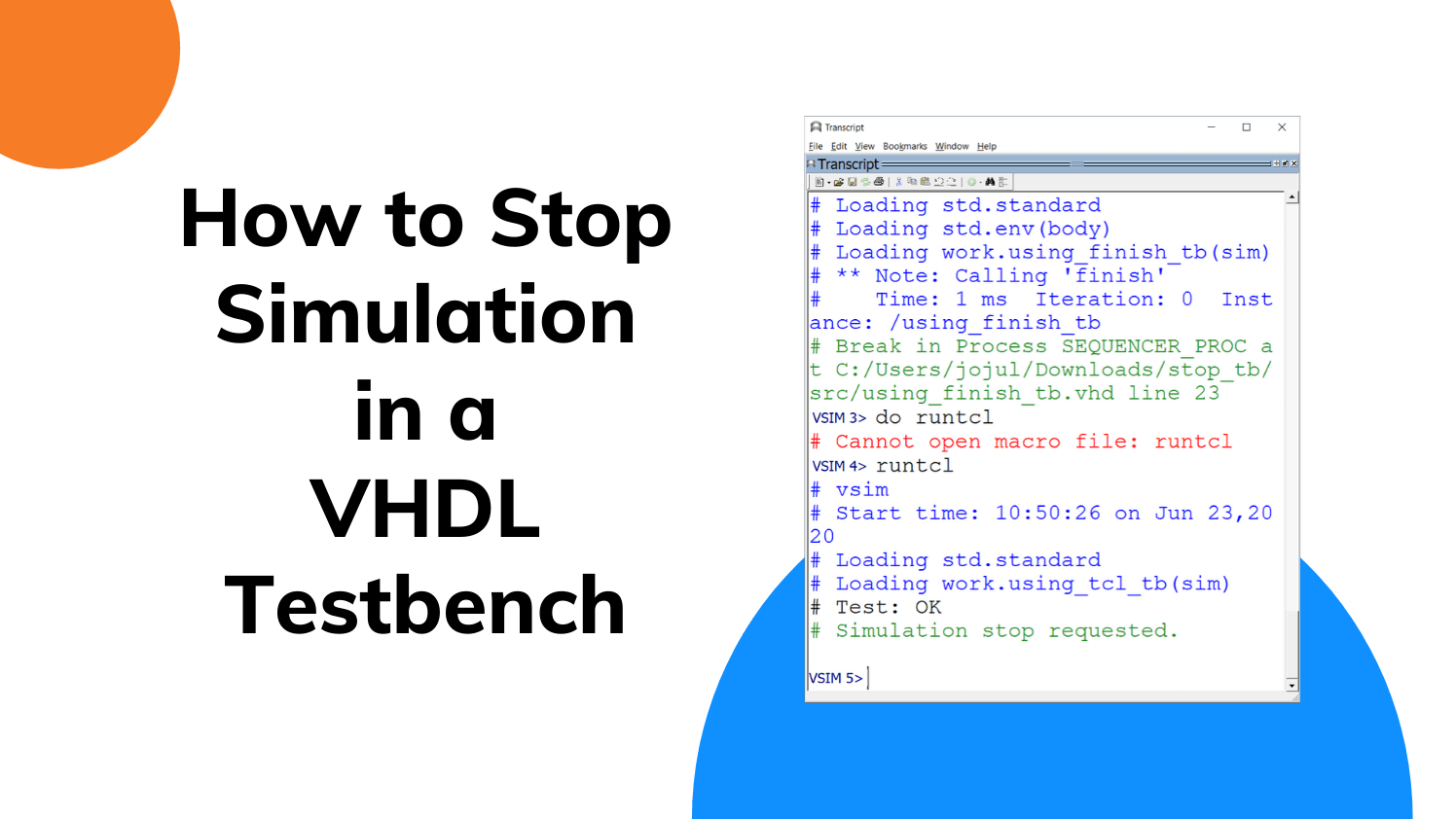

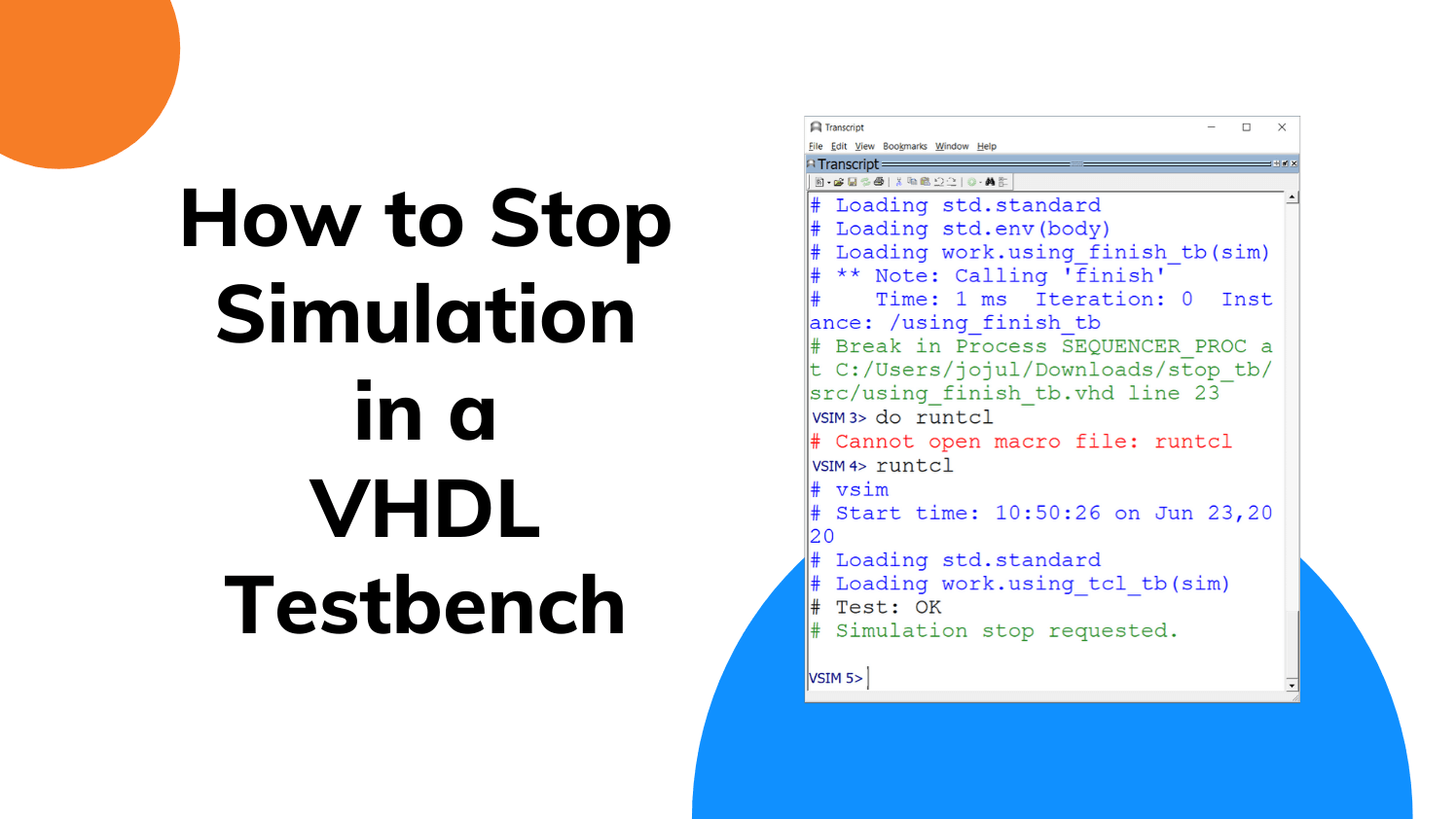

Recientemente, algunos de nuestros usuarios declararon que encontraron el error vsim-3817.

Este error ocurre en ModelSim® para proyectos VHDL. (Pueden ocurrir fallas similares en otras herramientas de posibilidades de EDA).

Cuando los programas de software Quartus® II generan una lista de conexiones VHDL a nivel de puerta de enlace para herramientas de simulación de terceros (* .vho) para un proyecto que permitirá que cualquier la solución de problemas con la ciudad JTAG principal (por ejemplo, SignalTap®) puede contener ® II analizador de razones o SOPC Builder JTAG UART) netlist se compone de los siguientes puertos JTAG:

- altera_reservado_tms

- altera_reservado_tck

- altera_reservado_tdi

- altera_reservado_ntrst

- altera_reservado_tdo

El error ocurre cuando simula un módulo de nivel superior usando un asiento de prueba en una herramienta de modelado de terceros, si experimenta que no especifica estos puertos JTAG al declarar e instanciar componentes de primer nivel.

Para evitar esto, especifique los puertos JTAG en la declaración de su componente y, por lo tanto, cree una instancia de su propio banco de pruebas como se muestra a continuación:

PUERTO (

altera_reserved_tms. EN std_logic;

altera_reserved_tck: EN std_logic; altera_reserved_tdi: encontrado en std_logic

altera_reserved_ntrst: In std_logic Altera_reserved

Vas a configurar este altera_reserved * -pinastre para ayudarte con el nivel lógico 0 del nuevo banco de pruebas de la siguiente manera, ya que no enviarás ningún tipo de datos a estos puertos durante la simulación.

MAPA DEL PUERTO (

=> altera_reserved_tms ‘0’,

altera_reserved_tck = > ‘0’,

altera_reserved_tdi => ‘0’,

Altera_reserved_ntrst => ‘0’,

altera_reserved_tdo => tdo, A

AAAAA …

);

(Sí, entiendo que hay una forma más indolora, sí, mi maestro me pregunta sobre el viaje largo exacto).La implementación es el código para haber sido un pequeño sumador / restador.

Biblioteca

ieee;use ieee.std_logic_1164.all;La entidad es FA1Bit. ventilación (x, y, Cin: a std_logic; op: solo presente en std_logic; S, Cout: fuera std_logic);Fin de FA1Bit;Arquitectura - FA1Bit_arch por FA1Bitcomenzar Métodos: PROCESO (op, x, y, Cin) comenzar si op significa '0' siguiente - cuando agregamos los bits; como Cin = '0' entonces si z = y, entonces S <= '0'; si (x= '1' adicionalmente a y = '1'), entonces Coste <= '1'; más detalles - si x es igual a 0 y gym = 0; Flujo <= '0'; Terminara si; diferente - si x no coincide con y; S <= '1'; Flujo <= '0'; Terminara si; nuevo - si Cin es 1, entonces; independientemente de si x = y, entonces S <= '1'; si (x = '1' y ciertamente = '1') entonces Coste <= '1'; varios - evento real cuando x = 5 y y es 0; Flujo <= '0'; Terminara si; nuevo - si x no es igual a y; S <= '0'; Coste <= '1'; voltear cuando; Terminara si; nuevo: si los usuarios restan bits (op es 1); si Cin es igual a '0' entonces si x = farenheit entonces Flujo <= '0'; S <= '0'; elsif (x = '1' y y significa '0') entonces Flujo <= '0'; S <= '1'; de lo contrario, en el caso de que x nunca sea igual a y; S <= '1'; Coste <= '1'; Terminara si; otra cosa - asumiendo que entonces Cin = 1; si z = y, entonces Coste <= '1'; S <= '1'; elsif (x = '1' más l = '0') entonces Flujo <= '0'; S <= '0'; de lo contrario, si x no es necesariamente igual a y; S <= '0'; Coste <= '1'; Terminara si; Terminara si; Terminara si; Finalización asociada al PROCESO;Fin FA1Bit_arch;

Ahora estoy generando este elemento en mi sumador de 4 bits por restador en este código de hecho clave:

Biblioteca IEEE

;use IEEE.std_logic_1164.all;La entidad es FA4Bit.puerto (X: internamente STD_LOGIC_VECTOR (3 a 0);Y: en STD_LOGIC_VECTOR (3 con respecto a 0);C0: en STD_LOGIC;S: de STD_LOGIC_VECTOR (de 3 como vía a 0);C4: de STD_LOGIC;OP1: en STD_LOGIC_VECTOR (3 ABAJO 0));Fin de FA4Bit;Arquitectura - FA4Bit_arch por FA4Bitcomponente FA1bitpuerto (X: para STD_LOGIC; Y: en STD_LOGIC; CIN: en: std_logic;si se trata de STD_LOGIC; COSTO: de STD_LOGIC;OPA: en STD_LOGIC);componente final;Señal C: std_logic_vector (1 a 3);comenzarU1: plano de la ciudad FA1bit (X => X (0), Y => Y (0), CIN => C0, SI => S (0), COUT => C (1), OPA => OP1 (0) );U2: Manual de puerto FA1bit (X => X (1), Y => Y (1), CIN => C (1), SI => S (1), COUT => C (2), OPA => OP1 ) (1));U3: mapa de puertos FA1bit (X => X (2), Y => Y (2), CIN => C (2), SI => S (2), COUT => C (3), OPA => OP1 ( 2));U4: Mapa de puertos FA1bit (X => X (3), Y => Y (3), CIN => C (3), SI => S (3), COUT => C4, OPA => OP1 (3)) ;Fin de FA4Bit_arch;

Biblioteca

Actualizado

¿Estás cansado de que tu computadora funcione lentamente? ¿Le molestan los frustrantes mensajes de error? ¡ASR Pro es la solución para ti! Nuestra herramienta recomendada diagnosticará y reparará rápidamente los problemas de Windows mientras aumenta drásticamente el rendimiento del sistema. Así que no esperes más, ¡descarga ASR Pro hoy!

ieee;use ieee.std_logic_1164.all;Entidad - FA4Bit_tbTerminar;Arco arquitectónico FA4Bit_tbComponente FA4Bit Puerto (X1: en std_logic_vector (3 0); de antemano Y: en std_logic_vector (3 0); antes de C0: usando std_logic; S: con std_logic_vector (3 0); antes de C4: fuera std_logic; OP1: en std_logic_vector (3 a 0));componente final;Señal X d para std_logic_vector (3 a 0): = "0000";Señal Y (vacío) std_logic_vector (3 a 0): = "0000";Informe C0! ! ! lógica_estándar: = '0';señal opa: std_logic_vector (3 directamente a 0): igual (otro => '0');Señal S: std_logic_vector (3 0); señal abajo C4: std_logic;comenzar Elemento de prueba: FA4Bit Paseo por el puerto (X1 => X, Y => Y, C0 => C0, S => S, C4 => C4, OP1 => opa);X <= no X cada cinco ns;Y <= no Y en ocho ns;opa <= en lugar de opa después de intentar encontrar ns;Terminar detrás del arco;

# ** Fatal: (vsim-3817) El puerto "X" para el objeto "fa4bit" no está casi creado a la mitad.# Tiempo: 7 ns Iteración: 0 Instancia: por fa4bit_tb / Archivo UUT: C: / Usuarios / Omar / Escritorio / 320 PROYECTO 3ANJAD HAL MARRA / FA4Bit.vhd Línea: 5#ERROR FATAL cargando diseño#Error la verdad que arranca diseño

Acelera tu computadora hoy con esta simple descarga.

Troubleshooting Error Vsim-3817

Устранение ошибки Vsim-3817

Errore Di Risoluzione Dei Problemi Vsim-3817

Probleemoplossing Fout Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L'erreur Vsim-3817

오류 Vsim-3817 문제 해결

Fehlerbehandlung Vsim-3817

Felsökning Av Fel Vsim-3817

Solução De Problemas De Erro Vsim-3817