Table of Contents

Uppdaterad

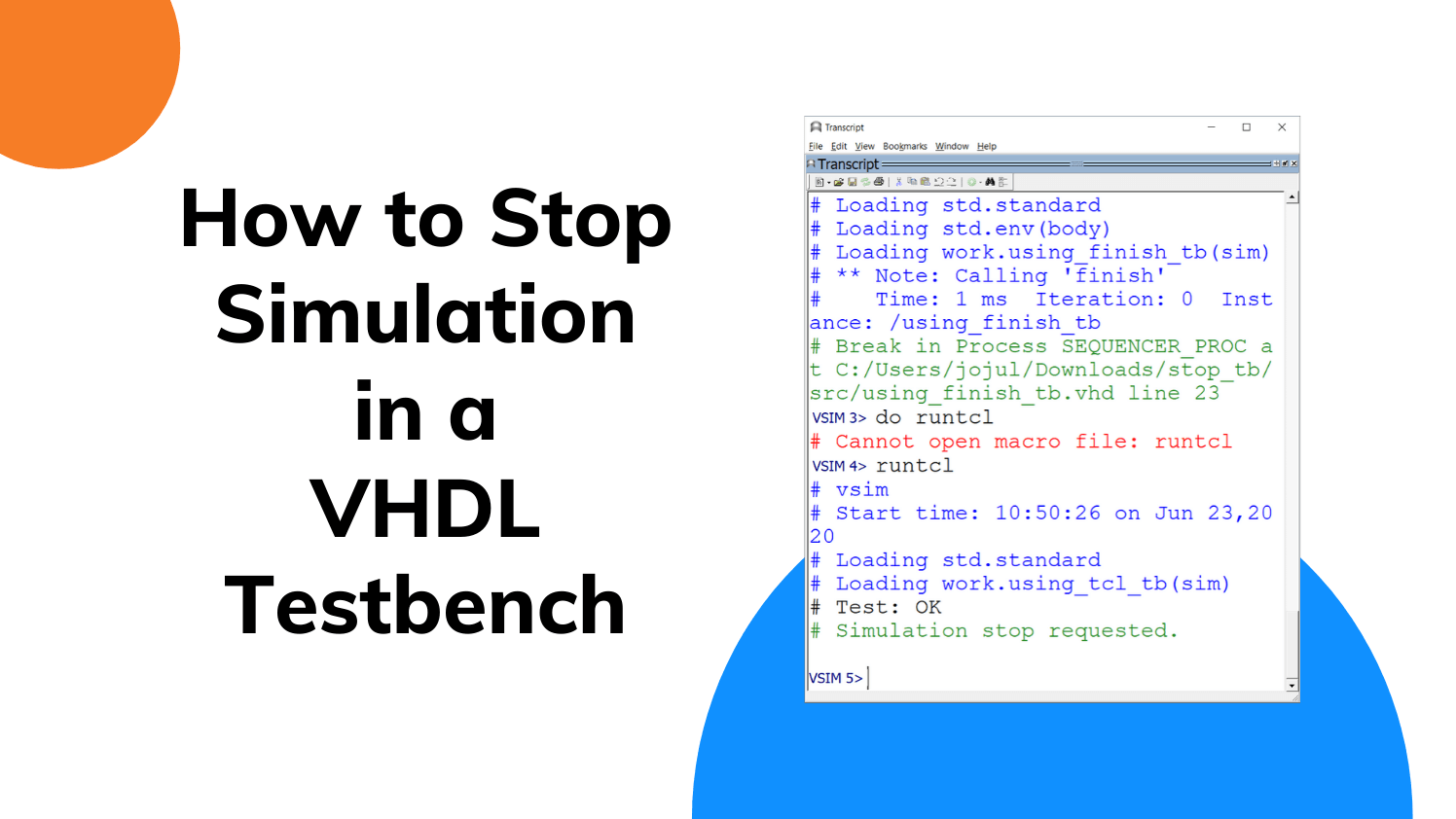

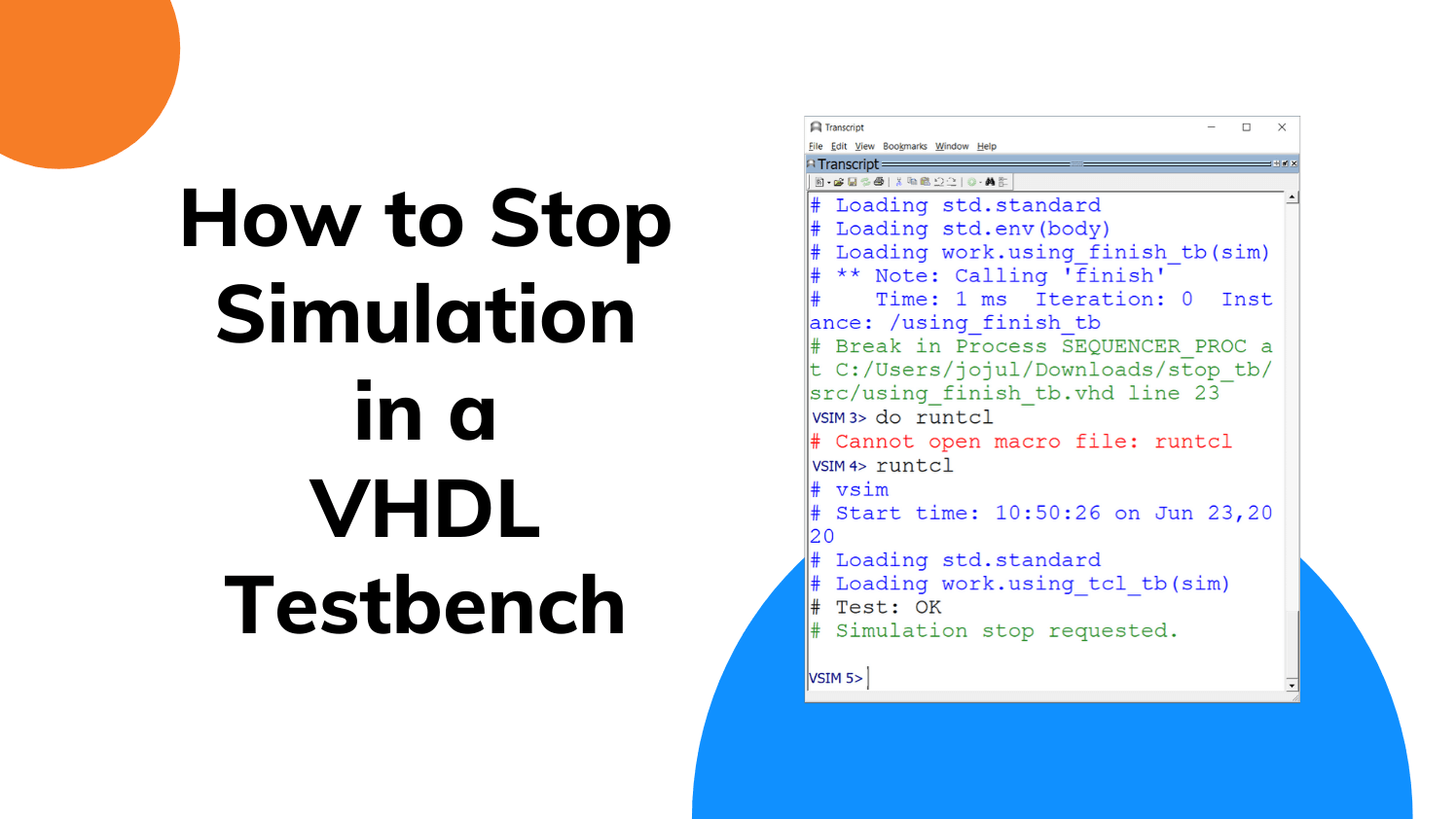

Nyligen rapporterade några av våra användare att de stötte på fel vsim-3817.

Det här felet resulterar i ModelSim® för VHDL-projekt. (Liknande fel kan uppstå i andra EDA-modelleringsverktyg.)

När Quartus® II-mjukvaran genererar den senaste VHDL-nätlistan på gateway-nivå för simuleringsmetoder från tredje part (* .vho) för ett projekt som tillåter alla specifika on-chip felsökning med den primära JTAG-porten (t.ex. SignalTap®) kan innehålla ® II logikanalysator eller SOPC Builder JTAG UART) nätlistan innehåller de använda JTAG-portarna:

- altera_reserved_tms

- altera_reserved_tck

- altera_reserved_tdi

- altera_reserved_ntrst

- altera_reserved_tdo

Felet uppstår när du simulerar varje toppnivåmodul med en testbänk i ett verkligt tredjepartsmodelleringsverktyg, om du inte anger dessa JTAG-portar när du deklarerar och instansiera komponenter på toppnivå.

För att undvika detta problem, specificera JTAG-portar i din komponentdeklaration och instansiera följaktligen din egen testbänk enligt nedan:

PORT (

altera_reserved_tms. IN std_logic;

altera_reserved_tck: IN std_logic; altera_reserved_logic: in std_reserved_logic;

altera_reserved_ntrst: In std_logic Altera_reserved

Du kan ställa in denna unika altera_reserved * -pinastre till intuition 0-nivån för den nya testbädden som den använder, eftersom du inte kommer att skicka några data för att hjälpa dessa portar under simulering .

PORTKARTA (

=> altera_reserved_tms ‘0’,

altera_reserved_tck = > ‘0’,

altera_reserved_tdi => ‘0’,

Altera_reserved_ntrst => ‘0’,

t altera_reserved_ => tdo, A

AAAAA …

);

(Ja, jag förstår att det finns ett enklare sätt, det finns, min lärare frågar mig om den långa resan.)Implementeringen är koden för min småskaliga adderare/subtraherare.

Bibliotek

ieee;använd ieee.std_logic_1164.all;Enheten är FA1Bit. port (x, ful, Cin: till std_logic; op: endast i std_logic; S, Cout: out std_logic);Slut på FA1Bit;Arkitektur - FA1Bit_arch skriven av FA1BitBörja Metoder: PROCESS (op, a, y, Cin) Börja om op betyder '0' då - om vi kanske lägger till bitarna; precis som Cin betyder '0' då om x = farrenheit, då S <= '0'; if (x= '1' och en ymca = '1'), då Kostnad <= '1'; lite mer detaljer - om x = 0 och som en konsekvens gym = 0; Strömma <= '0'; Sluta om; annat - i det fall att x inte matchar y; S <= '1'; Strömma <= '0'; Sluta om; annat - om Cin är 1, då; oavsett om x = y, då S <= '1'; i fallet (x = '1' och y betyder bara '1') då Kostnad <= '1'; annat än där - verklig händelse när x = 0 och p är 0; Strömma <= '0'; Sluta om; annat - om by inte är lika med y; S <= '0'; Kostnad <= '1'; likvidera när; Sluta om; ny - om du subtraherar bitar (op är 1); om Cin = '0' då om x = Fahrenheit då Strömma <= '0'; S <= '0'; elsif (x är lika med '1' och y = '0') då Strömma <= '0'; S <= '1'; annars, placerad i fallet när x inte är lika för att hjälpa dig till y; S <= '1'; Kostnad <= '1'; Sluta om; annat - antar att då Cin är lika med 1; om x = p oker, alltså Kostnad <= '1'; S <= '1'; elsif (x = '1' plus y betyder '0') då Strömma <= '0'; S <= '0'; bättre - om x inte är lika för att tillåta dem att y; S <= '0'; Kostnad <= '1'; Sluta om; Slut, Om; Sluta om; Slutförande av PROCESSEN;Avsluta FA1Bit_arch;

Jag använder nu denna bidragande faktor i min 4-bitars adderare/subtraherare och gör denna nyckelfaktakod:

IEEE bibliotek

;använd IEEE.std_logic_1164.all;Entiteten är FA4Bit.Hamn (X: inuti STD_LOGIC_VECTOR (3 till 0);Y: i STD_LOGIC_VECTOR (3 till 0);C0: under STD_LOGIC;S: från STD_LOGIC_VECTOR (från 3 till 0);C4: härrörande från STD_LOGIC;OP1: i STD_LOGIC_VECTOR (3 NED 0));Slut på FA4Bit;Arkitektur - FA4Bit_arch av FA4BitFA1bit komponentport (X: i STD_LOGIC; Y: i STD_LOGIC; CIN: i: std_logic;om på STD_LOGIC; KOSTNAD: från STD_LOGIC;OPA: i STD_LOGIC);Slutlig komponent;Signal C: std_logic_vector (1 till 3);BörjaU1: stadsplan FA1bit (X => X (0), Y => Y (0), CIN => C0, SI => S (0), COUT => C (1), OPA => OP1 (0) );U2: FA1bit plug-in manual (X => X (1), Y => Y (1), CIN => C (1), SI => S (1), COUT => C (2), OPA = > OPi) (1));U3: FA1bit Portmap (X => X (2), Y => Y (2), CIN => C (2), SI => S (2), COUT => C (3), OPA => OP1 ( 2));U4: FA1bit Portmap (X => X (3), Y => Y (3), CIN => C (3), SI => S (3), COUT => C4, OPA => OP1 (3)) ;Slut om FA4Bit_arch;

Bibliotek

Uppdaterad

Är du trött på att din dator går långsamt? Irriterad av frustrerande felmeddelanden? ASR Pro är lösningen för dig! Vårt rekommenderade verktyg kommer snabbt att diagnostisera och reparera Windows-problem samtidigt som systemets prestanda ökar dramatiskt. Så vänta inte längre, ladda ner ASR Pro idag!

ieee;använd ieee.std_logic_1164.all;Entitet - FA4Bit_tbAvsluta;Arkitektonisk båge FA4Bit_tbFA4Bit-komponent Port (X1: i std_logic_vector (3 0); före Y: insidan av std_logic_vector (3 0); före C0: via std_logic; S: med std_logic_vector (3 0); innan nu C4: ut std_logic; OP1: angående std_logic_vector (3 till 0));Slutlig komponent;Signal X dför std_logic_vector (3 till 0): = "0000";Signal Y (tom) std_logic_vector (3 till 0): = "0000";Rapportera C0! , ! std_logic: = '0';opa-signal: std_logic_vector (3 till faktiskt 0): lika (annan => '0');S-signal: std_logic_vector (3 0); kupong ner C4: std_logic;Börja Testobjekt: FA4Bit Port tourelle (X1 => X, Y => Y, CO => CO, S => S, C4 => C4, OP1 => opa);X <= inte X var femte ns;Y <= ska inte Y i åtta ns;opa <= verkligen opa efter att ha försökt hitta ns;Änden av bågen;

# ** Fatal: (vsim-3817) Port "X" med avseende på objektet "fa4bit" är inte halvt skapad.# Tid: 6 ns Iteration: 0 Instans: / fa4bit_tb / UUT-fil: C: / Användare / Omar / Desktop / 320 PROJEKT 3ANJAD HAL MARRA / FA4Bit.vhd Rad: 5#FATALT FEL vid laddning av design# Fel vid startpunktsdesign

Få fart på din dator idag med denna enkla nedladdning.

Troubleshooting Error Vsim-3817

Устранение ошибки Vsim-3817

Errore Di Risoluzione Dei Problemi Vsim-3817

Probleemoplossing Fout Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L’erreur Vsim-3817

오류 Vsim-3817 문제 해결

Solución De Problemas De Error Vsim-3817

Fehlerbehandlung Vsim-3817

Solução De Problemas De Erro Vsim-3817