Table of Contents

업데이트됨

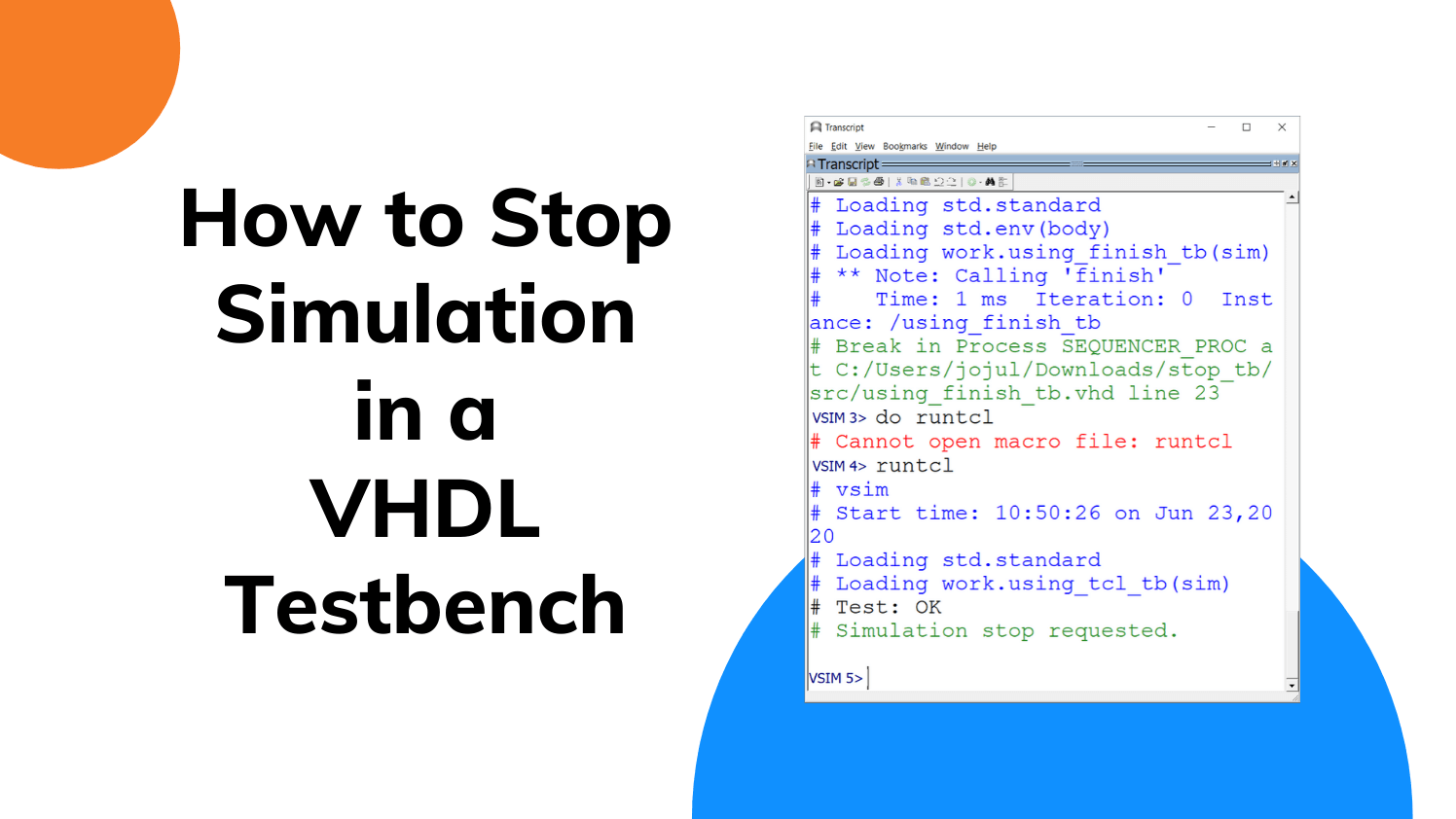

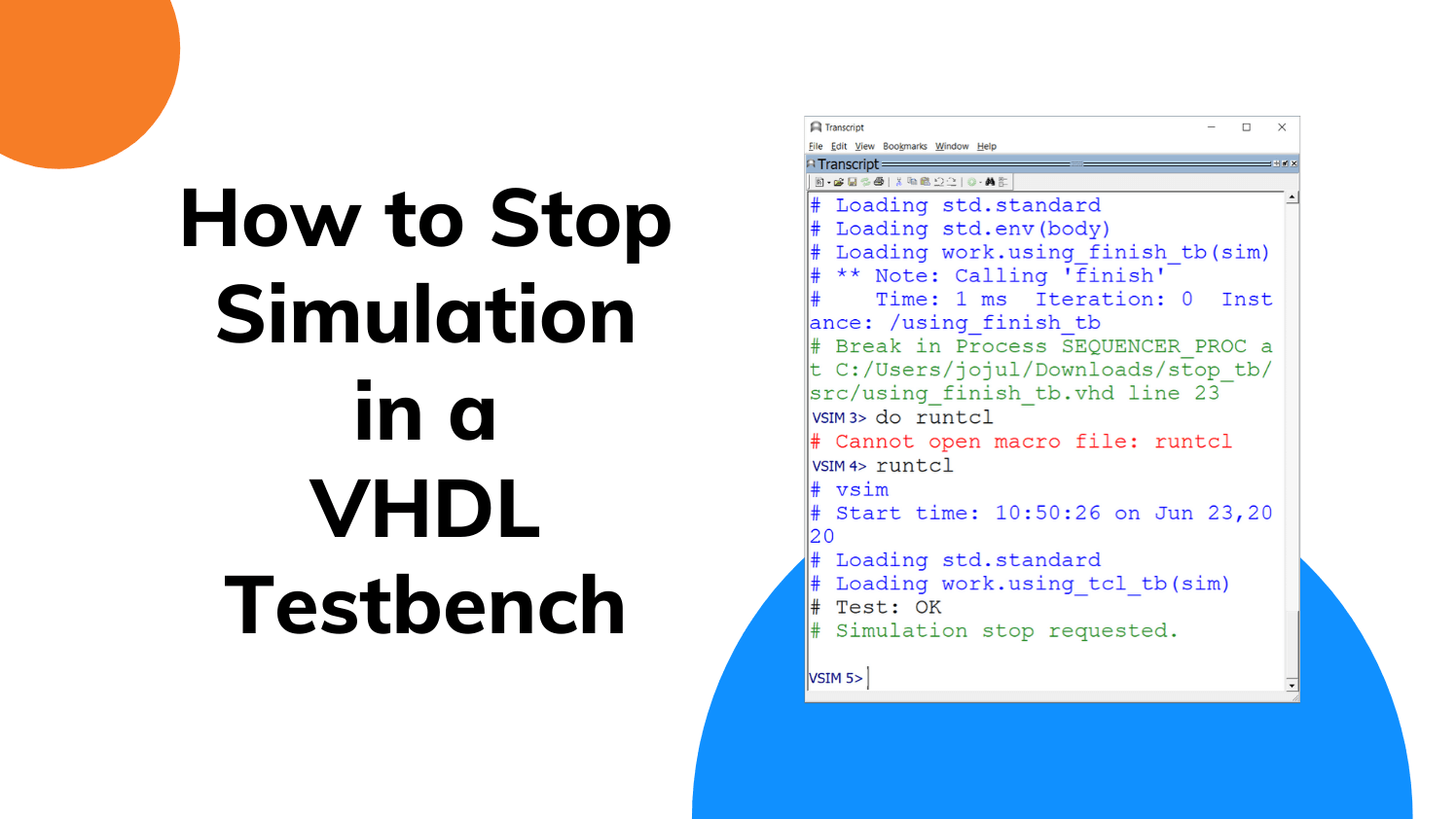

최근에 일부 인터넷 마케팅 담당자가 vsim-3817 오류가 발생했다고 보고했습니다.

이 오류는 VHDL 계획용 ModelSim®에서 발생합니다. (다른 EDA 패터닝 도구에서도 유사한 오류가 발생할 수 있습니다.)

Quartus® II 소프트웨어가 종종 모든 온-오프 기본 JTAG 포트(예: SignalTap®)를 사용한 칩 문제 해결에는 ® II 직관 분석기 또는 SOPC Builder JTAG UART가 포함될 수 있습니다. 넷리스트에는 다음 JTAG 포트가 포함됩니다.

- altera_reserved_tms

- altera_reserved_tck

- altera_reserved_tdi

- altera_reserved_ntrst

- altera_reserved_tdo

타사 모델링 도구에서 평가 벤치를 사용하여 최상위 모듈을 시뮬레이션할 때 회사에서 청구할 때 이러한 JTAG 포트를 지정하지 않으면 오류가 발생합니다. 및 최상위 구성 요소를 인스턴스화합니다.

이 기술 문제를 피하려면 구성 요소 팩트에 JTAG 포트를 지정하고 아래에 표시될 때마다 고유한 테스트 벤치를 인스턴스화하십시오.

COMPONENT

이 altera_reserved 를 설정할 수 있습니다 4 . - 시뮬레이션 동안 이 포트에 데이터를 전달하지 않을 것이기 때문에 다음과 같이 새로 발견된 테스트베드의 로직 0 레벨로 pinastre.

<코드> <인스턴스 이름>: <객체 이름>

포트 맵(

=> altera_reserved_tms '0',

altera_reserved_tck => '0',

altera_reserved_tdi => '0',

Altera_reserved_ntrst => '0',

tadoreserved _ altera_reserved_tdi => '0',

=> tdo, A

AAAAAA ...

);

(예, 더 쉬운 방법이 있다는 것을 이해합니다. 예, 선생님이 긴 여정이 필요한지 묻습니다.)구현은 내 작은 가산기/뺄셈기 때 코드입니다.

라이브러리

ieee;ieee.std_logic_1164.all을 사용하십시오.엔티티는 FA1Bit입니다. 열기(x, y, Cin: std_logic으로; op: 순전히 std_logic에서; S, Cout: out std_logic);FA1Bit의 끝;아키텍처 - FA1Bit의 FA1Bit_arch시작하다 방법: PROCESS(op, x, y, Cin) 시작하다 op 자원이 '0'이면 - 비트를 추가할 때; Cin = '0'만 포함하면 x = y이면 S <= '0'; if (x= '1' 및 결과적으로 a y = '1'), 다음 비용 <= '1'; 자세한 내용 - y = 0이고 체육관 = 0인 경우; 스트림 <= '0'; 종료 더 이상 - x가 y를 이기지 않으면; S <= '1'; 스트림 <= '0'; 종료 다양한 - Cin이 1이면; x = s인지 여부에 관계없이 S <= '1'; if (x = '1'이고 b는 그냥 = '1') 그러면 비용 <= '1'; else - x가 0이고 y가 0일 때 실제 이벤트. 스트림 <= '0'; 종료 이것들이 아닌 경우 - x가 같지 않으면 y가 됩니다. S <= '0'; 비용 <= '1'; 언제 뒤집다; 종료 new - 비트를 빼거나 뺄 때(op는 1); Cin이 '0'인 경우 x가 화씨와 같으면 스트림 <= '0'; S <= '0'; elsif (x = '1'이고 y는 '0'과 같습니다) 그러면 스트림 <= '0'; S <= '1'; 그렇지 않으면 x가 y와 거의 같지 않은 경우; S <= '1'; 비용 <= '1'; 종료 else - 아이디어를 가정하면 Cin = 1; x = y와 마찬가지로 비용 <= '1'; S <= '1'; elsif (x = '1'과 y = '0' 결합) 스트림 <= '0'; S <= '0'; else - x가 항상 y와 같지 않은 경우; S <= '0'; 비용 <= '1'; 종료 종료, 경우; 종료 프로세스 완료FA1Bit_arch 종료;

따라서 이 핵심 사실 코드의 4가지 가산기/감산기에서 이 요소를 사용하고 있습니다.

IEEE 라이브러리 <사전> <코드>;IEEE.std_logic_1164.all을 사용하십시오.엔티티는 FA4Bit입니다.항구(X: STD_LOGIC_VECTOR 내부(3에서 0);Y: STD_LOGIC_VECTOR에서 (3에서 0);C0: STD_LOGIC에서;S: STD_LOGIC_VECTOR에서 (에서 0으로);C4: STD_LOGIC에서;OP1: STD_LOGIC_VECTOR에서 (3 DOWN 0));FA4Bit의 끝;아키텍처 - FA4Bit의 FA4Bit_archFA1bit 컴포넌트포트(X: STD_LOGIC, Y: STD_LOGIC, CIN: 입력: std_logic,STD_LOGIC에 있는 경우; 비용: STD_LOGIC에서;OPA: STD_LOGIC에서);최종 구성 요소;신호 C: std_logic_vector(1 ~ 3);시작하다U1: 도시 배열 FA1비트(X => X(0), Y => Y(0), CIN => C0, SI => S(0), COUT => C(1), OPA => OP1(0) );U2: FA1bit 포트 수동(X => X(1), Y => Y(1), CIN => C(1), SI => S(1), COUT => C(2), OPA => OP1 ) (1));U3: FA1비트 포트맵(X => X(2), Y => Y(2), CIN => C(2), SI => S(2), COUT => C(3), OPA => OP1( 2));U4: FA1비트 포트맵(X => X(3), Y => Y(3), CIN => C(3), SI => S(3), COUT => C4, OPA => OP1(3)) ;FA4Bit_arch의 끝; 라이브러리

업데이트됨

컴퓨터가 느리게 실행되는 것이 지겹습니까? 실망스러운 오류 메시지에 짜증이 납니까? ASR Pro은 당신을 위한 솔루션입니다! 우리가 권장하는 도구는 시스템 성능을 극적으로 향상시키면서 Windows 문제를 신속하게 진단하고 복구합니다. 그러니 더 이상 기다리지 말고 지금 ASR Pro을 다운로드하세요!

ieee;ieee.std_logic_1164.all을 사용하십시오.엔티티 - FA4Bit_tb마치다;건축 아치 FA4Bit_tbFA4Bit 구성 요소 포트(X1: std_logic_vector(3 0)); 사전에 Y: std_logic_vector(3 0)에서; C0 이전: std_logic을 통해; S: std_logic_vector(3 0)로 작업 C4 이전: std_logic 출력; OP1: std_logic_vector에서 (3에서 0));최종 구성 요소;std_logic_vector에 대한 신호 X d(3에서 0): "0000"과 동일합니다.신호 Y(비어 있음) std_logic_vector(3에서 0): "0000"을 의미합니다.신고 C0! ! ! std_logic: = '0';opa 신호: std_logic_vector(3에서 0): 같음(기타 => '0');S 스틱: std_logic_vector(3 0); 신호 다운 C4: std_logic;시작하다 테스트 항목: FA4Bit 항구 투어 (X1 => X, Y => Y, C0 => C0, S => S, C4 => C4, OP1 => opa);X <= X가 아님 거의 5ns;Y <= 동작 ns에서 Y가 아님;opa <= ns 획득을 시도한 후 opa가 아닙니다.호의 끝;

# ** 치명적: (vsim-3817) "fa4bit" 개체에 대한 "X" 포트가 생성되지 않았습니다.# 시간: 7ns 반복: 0 인스턴스: 또는 fa4bit_tb / UUT 파일: C: / 사용자 대 Omar / 데스크탑 / 320 PROJECT 3ANJAD HAL MARRA / FA4Bit.vhd 행: 5#FATAL ERROR 충전 디자인# 디자인 시작 중 오류

오늘 이 간단한 다운로드로 컴퓨터 속도를 높이십시오. 년

Troubleshooting Error Vsim-3817

Устранение ошибки Vsim-3817

Errore Di Risoluzione Dei Problemi Vsim-3817

Probleemoplossing Fout Vsim-3817

Rozwiązywanie Problemów Z Błędem Vsim-3817

Dépannage De L'erreur Vsim-3817

Solución De Problemas De Error Vsim-3817

Fehlerbehandlung Vsim-3817

Felsökning Av Fel Vsim-3817

Solução De Problemas De Erro Vsim-3817

년