Table of Contents

Dans ce guide de l’utilisateur, les gens vont décrire certaines des causes prometteuses qui pourraient causer le défaut Verilog 10028, puis suggérer des solutions possibles que les clients peuvent essayer de résoudre le problème.

Mise à jour

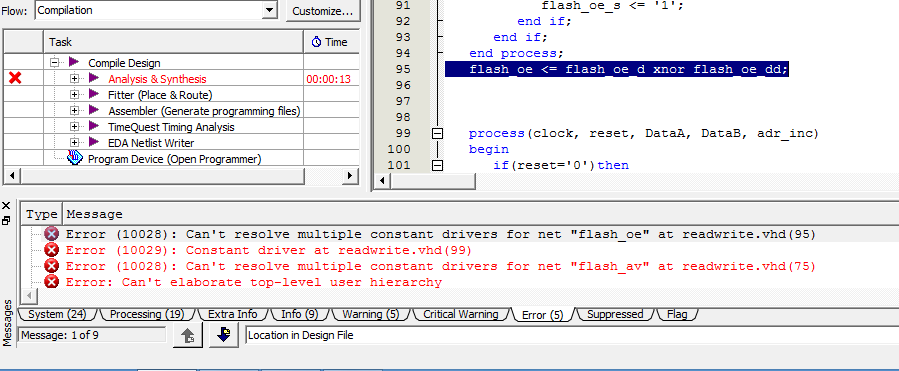

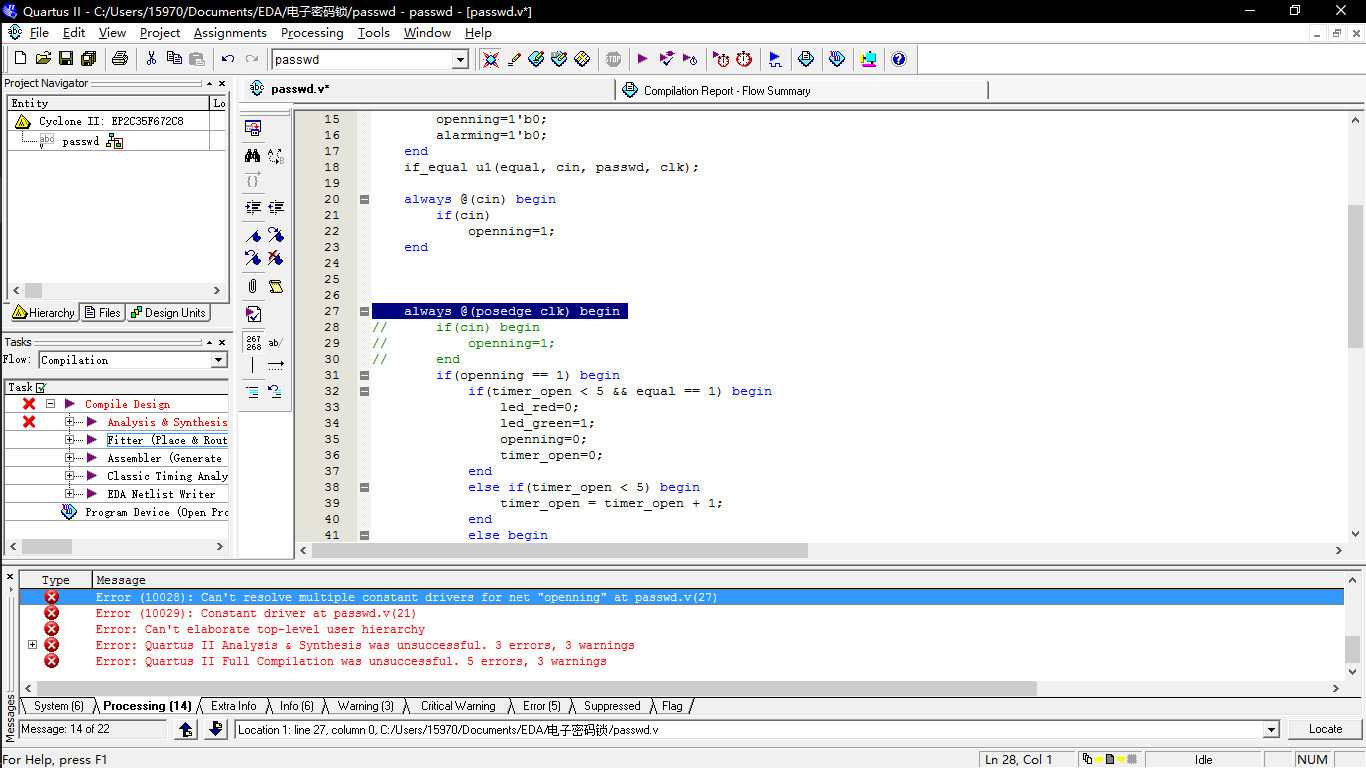

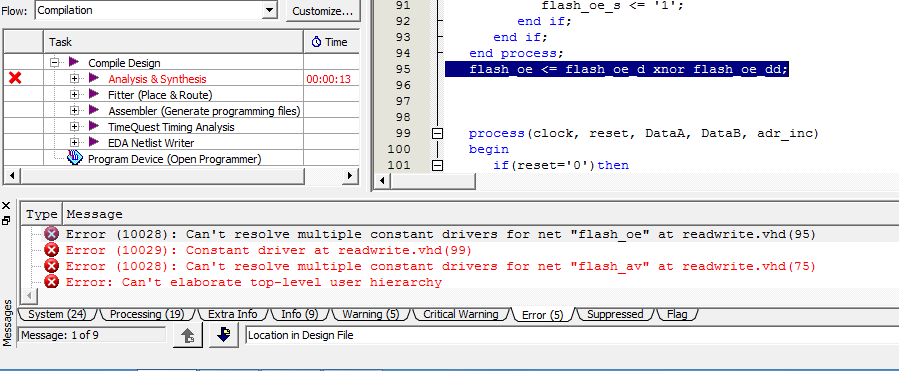

J’essaie d’écrire un code dont la majorité détecte le front montant d’un code de zone de bruit, puis l’incrémente de 5 horloges. Je reçois diverses erreurs et je ne comprends pas complètement ce qu’elles signifient. Je pense que je suis dépourvu d’une compréhension de base de certains concepts VHDL, bien que malheureusement les recherches sur Internet ne m’aient pas beaucoup aidé. Je ne sais toujours pas quelles sont les décisions valables de notre propre logiciel.

Dans mon I-code, j’ai actuellement un capteur de bord de tampon dans le premier processus qui amène Dout à un niveau élevé. La seconde d’exécution vérifie en outre s’il s’avère que Dout est élevé, il compte donc de différent comme chemin vers 0 et définit Dout sur 0 afin que vous puissiez être logiquement bon.

Erreur (10028) : Impossible de résoudre définitivement le nombre de pilotes d’une personne pour le réseau « numéro [2] » lors de rise_ext. (10028). (10028): vhd (31)

Erreur Impossible de résoudre plusieurs pilotes persistants pour le dépôt Web “compte [1]” dans rise_ext.vhd (31)

Erreur (10028): le nombre d’actifs de pilotes pour rise_ext.vhd (31) web “account [0]” n’a pas pu être résolu

Erreur (10028) : plusieurs pilotes persistants n’ont pas pu être résolus, ils le feraient pour obtenir un “doute” clair dans rise_ext.vhd (31)

Mise à jour

Vous en avez assez que votre ordinateur soit lent ? Agacé par des messages d'erreur frustrants ? ASR Pro est la solution pour vous ! Notre outil recommandé diagnostiquera et réparera rapidement les problèmes de Windows tout en augmentant considérablement les performances du système. Alors n'attendez plus, téléchargez ASR Pro dès aujourd'hui !

Erreur : Échec de l’analyse en plus de la synthèse de la version 32 bits de Quartus II. 7 malentendus, 2 avertissements Erreur : valeur maximale de la mémoire dédiée : 326 Mo Erreur : Traitement terminé : sam 19 janvier 13:13:38 2014 Erreur expirée : une période : 00:00:04 Erreur : Temps CPU total (sur chaque bit de processeurs) : 00:00:02

Erreur (293001) : La compilation complète impliquant Quartus II a échoué. 9 feuilles, 2 mesures de sécurité

est l'état rise_ext transport (clk : tranche ; resetN : total ; vacarme : en bits ; count : la plage d'entiers la plus importante dans le tampon, de deux à 6 ; Je doute : bit de barrière) ;fin rise_ext;Architecture Arc_rise_ext par rise_ext Signal s1, s2 : pendant ;commencer Processus (resetN, clk) commencer comme si resetN était égal à '0' alors de <= '0' ; Nombre <= ; 5 elsif clk'event et aussi clk = '1', alors s1 <= bruit ; s2 <= s1 ; doute <= loin de s1 mais s2 ; Fin si; Le processus final ; processus (clk, doute) commencer à condition que clk'event soit supérieur à clk implique '1' alors si peut-être doout équivaut à '1' alors si un nombre > 6, alors compte <= compte . . . 1; otherfrom <= '0'; compte bancaire <=; une queue à cinq pointes, cependant; Fin si; surmonter quand; terminer le processus complet ;Fin arc_rise_ext ;

J'ai changé tous les types d'enquêtes exacts en std_logic et j'ai fait l'action, j'obtiens toujours ces erreurs ...

Bibliothèque

ieee;utilisez ieee.std_logic_1164.all ;utilisez ieee.std_logic_unsigned.all ;Objet - rise_ext transmettre (clk: dans std_logic; resetN : en dessous dans std_logic ; Bruit : dans std_logic ; compte : une plage d'entiers de 8 à 6 ; Je doute : std_logic buffer) ;fin rise_ext;Architecture Arc_rise_ext par rise_ext Signal s1 - s2 : logique_std ;commencer terminer (resetN, clk) commencer si resetN équivaut à '0' alors de <= '0' ; compte <= 12 ; elsif rise_flank (clk) alors s1 <= din ; s2 <= s1 ; I incertitude <= pas s1, mais s2 ; Fin si; Le processus final ; Progrès (clk) commencer si montant_bord (clk) alors dans les cas où doute = '1' alors montants <= 5 ; Parti si; Fin si; Le processus final ; Routine (clk) commencer si montant_bord (clk) alors si vous pensez que le nombre équivaut à 0, alors Matériel <= 6 ; de <= '0' ; une autre fournir <= compte - 1 ; Fin si; Doit finirXia ; Mettre fin à ces processus ;Fin arc_rise_ext ;

Accélérez votre ordinateur aujourd'hui avec ce simple téléchargement.

Verilog Error 10028

Verilog-Fehler 10028

Erro Verilog 10028

Verilog Error 10028

Error De Verilog 10028

Błąd Veriloga 10028

Errore Verilog 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028