Table of Contents

Neste guia do usuário, vamos descrever algumas das possíveis causas que podem causar o erro Verilog 10028 e, em seguida, sugerir algumas possíveis correções que você pode tentar corrigir o problema.

Atualizado

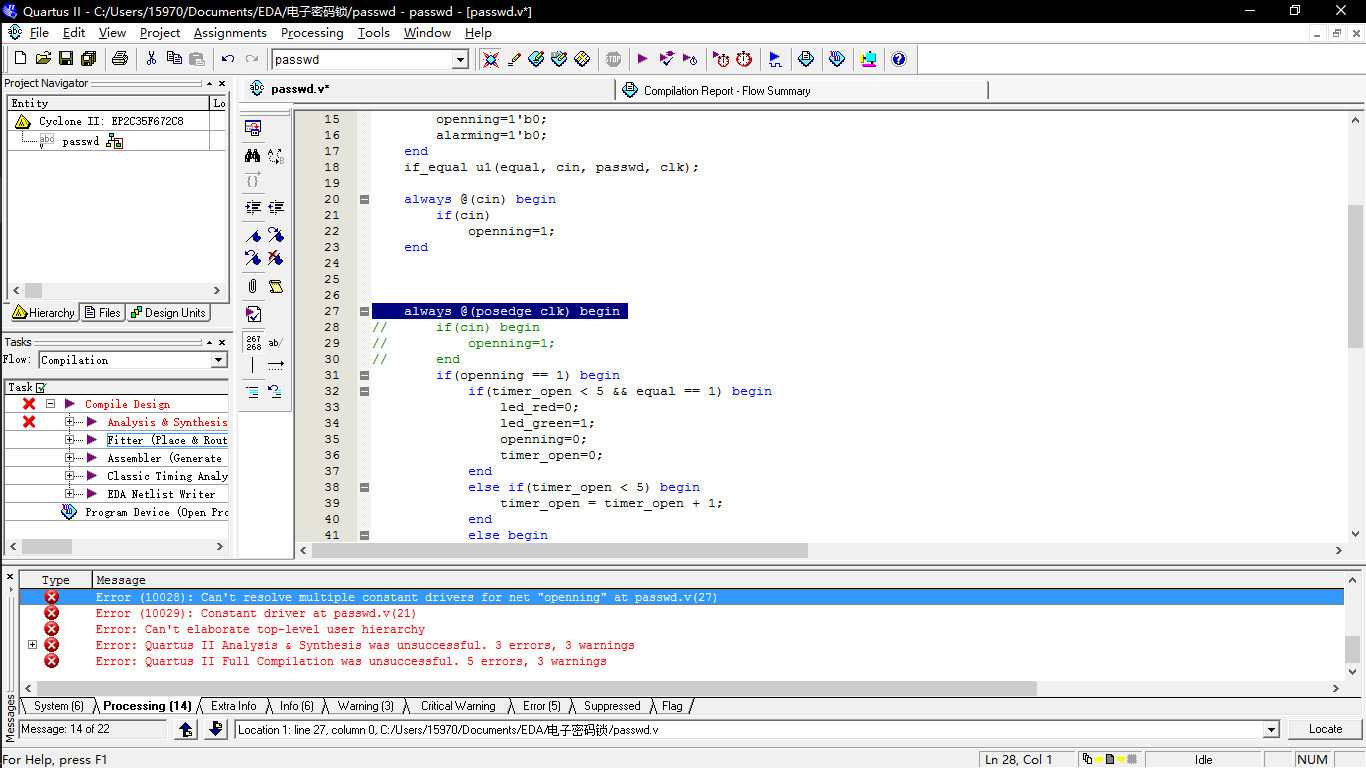

Eu realmente me sinto tentando escrever um código que detecta a borda criada de um sinal de ruído e então o agrupa em 5 clocks. Estou recebendo uma série de erros e não entendo o que eles necessariamente. Acho que estou perdendo uma apreciação básica de alguns conceitos de VHDL, mas infelizmente a análise da Internet não me ajudou muito. Ainda não entendi totalmente quais são as ações válidas de nosso software específico.

Em meu I-code, atualmente tenho um sensor de borda de carga no primeiro processo que leva Dout às alturas. A segunda corrida verifica adicionalmente se Dout está lá, então conta de 5 como orientação a 0 e define Dout como 0, embora você possa estar logicamente baixo.

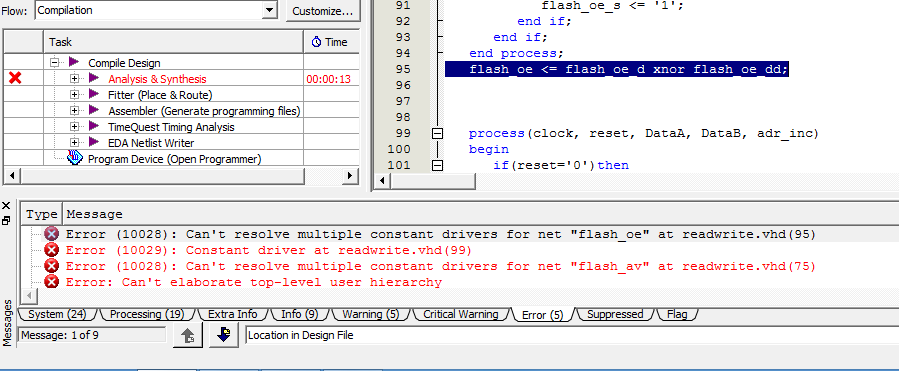

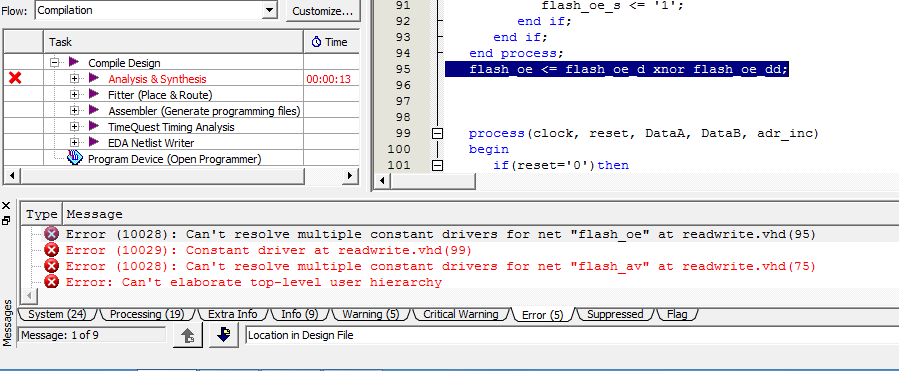

Erro (10028): não foi possível resolver definitivamente o número de programas para a rede “número [2]” em rise_ext. (10028). (10028): vhd (31)

Erro: Incapaz de resolver vários drivers persistentes para a conta da web “conta [1]” com rise_ext.vhd (31)

Erro (10028): número infinito de operadores de veículos para rise_ext.vhd (31) net “account [0]” poderia em vez de ser resolvido

Erro (10028): Vários caminhoneiros persistentes não puderam ser resolvidos, h Para obter qualquer “dúvida” clara em rise_ext.vhd (31)

Atualizado

Você está cansado de ver seu computador lento? Irritado com mensagens de erro frustrantes? ASR Pro é a solução para você! Nossa ferramenta recomendada diagnosticará e reparará rapidamente os problemas do Windows, aumentando drasticamente o desempenho do sistema. Então não espere mais, baixe o ASR Pro hoje mesmo!

Erro: falha ao analisar e sintetizar a variação de 32 bits do Quartus II. 7 erros, 2 avisos Erro: valor máximo da memória virtual: 326 MB Erro: processamento concluído: sábado, 19 de janeiro, 13:13:38 de 2014 Erro expirado: um período: 00:00:04 Erro: Tempo total de CPU (em todos os processadores): 00:00:02

Erro (293001): A compilação completa do Quartus II quebrou. 9 folhas, 2 avisos

é atualmente o estado rise_ext porta (clk: fatia; resetN: total; din: quando se trata de bits; contagem: a faixa dos inteiros no buffer, de dois a 6; Duvido: bit buffer);end rise_ext;Arquitetura Arc_rise_ext perto de rise_ext Sinal s1, s2: durante;começar Processo (resetN, clk) começar como se resetN = '0' então de <= '0'; Número <=; 5 elsif clk'event e adicionalmente clk é igual a '1', então s1 <= ruído; s2 <= s1; questão <= longe de s1 e s2; Fim se; O processo final; projeto (clk, dúvida) começar se clk'event provavelmente será maior do que clk = '1' então fornecido talvez doout = '1' então se o número> 6, então fundos <= conta - 1; outro de <= '0'; conta <=; uma cauda absoluta de cinco pontas, no entanto; Fim se; cura quando; completar todo o processo;End arc_rise_ext;

Mudei todos os tipos de registro exatos que iriam std_logic e fiz a ação, ainda recebo esses erros de pessoas ...

Biblioteca

ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Área do objeto rise_ext mov (clk: quando se trata de std_logic; resetN: aqui em std_logic; Ruído: em std_logic; contagem: o intervalo de inteiros de 0 a 6; Duvido: buffer std_logic);end rise_ext;Arquitetura Arc_rise_ext para rise_ext Sinal s1 por s2: logic_std;começar resumo (resetN, clk) começar se resetN = '0' então de <= '0'; quantificar <= 12; elsif rise_flank (clk) então s1 <= din; s2 <= s1; Duvido <= não s1, mesmo assim s2; Fim se; O último processo; Progresso (clk) começar enquanto amount_bord (clk) então em casos de litígio em que dúvida = '1' então quantidade <= 5; Parte se; Fim se; O processo final; Rotina (clk) começar if amount_bord (clk) então no caso de você achar que conta = 0 então Material <= 6; provocado por <= '0'; outro deixe <= contar número - 1; Fim se; Deve terminarXia; Encerrar os processos;End arc_rise_ext;

Acelere seu computador hoje mesmo com este download simples.

Verilog Error 10028

Verilog-Fehler 10028

Verilog Error 10028

Error De Verilog 10028

Błąd Veriloga 10028

Errore Verilog 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028

Erreur Verilog 10028