Table of Contents

I de här användartipsen kommer vi att beskriva några av er ser, de möjliga orsakerna som kan orsaka Verilog-felet 10028 och sedan föreslå några möjliga fixar det faktum att du kan försöka åtgärda problemet.

Uppdaterad

Jag försöker skriva riktnummer som upptäcker den stigande kanten på en ljudsignal och sedan ökar den med 5 lampor. Jag får olika fel och förstår inte vad de betyder. Jag tror att jag saknar en grundläggande förståelse för vissa VHDL-konceptdesigner, men tyvärr har internetforskning inte hjälpt mig så mycket. Jag vet fortfarande inte vad vår egen programvara har för verklighet.

I min I-kod har jag för närvarande en lastkantsensor i den första processen som kommer att driva Dout högt. Den andra körningen kontrollerar dessutom om Dout är hög, så det räknas som 5 som vägen till 0 och enheter Dout till 0 så att du kan vara pragmatiskt låg.

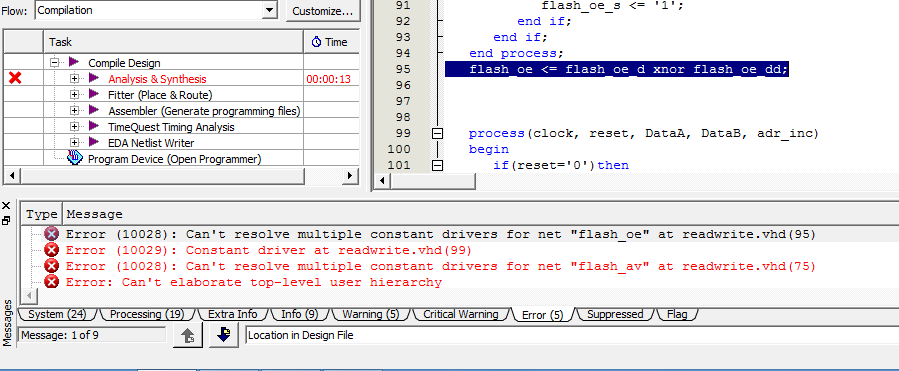

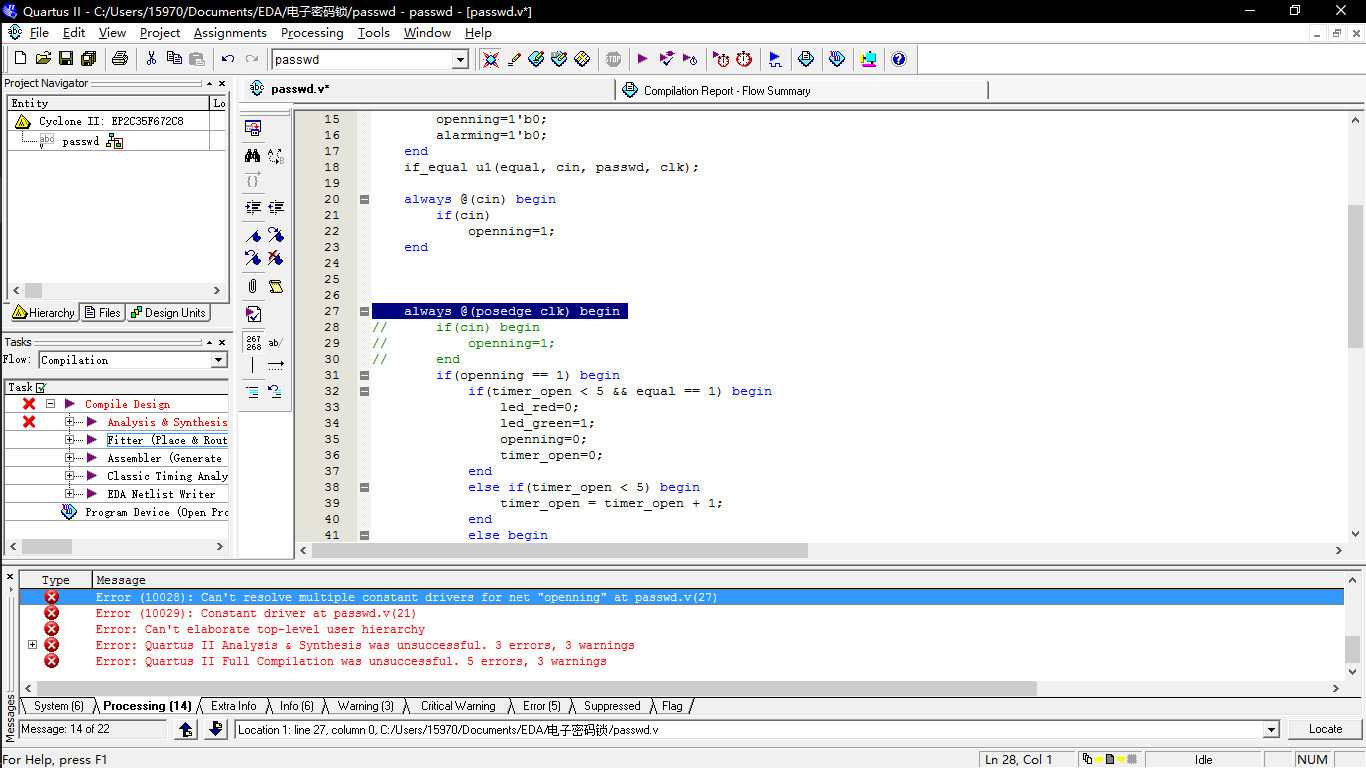

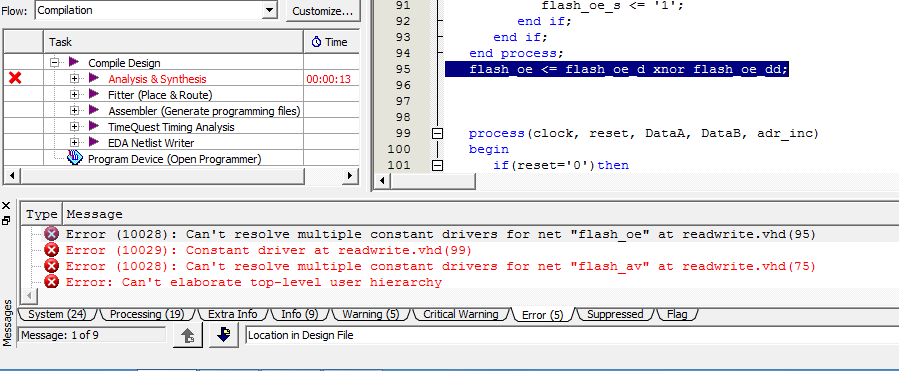

Fel (10028): Kan inte definitivt eliminera antalet drivrutiner för nätverket “nummer [2]” nära rise_ext. (10028). (10028): vhd (31)

Fel Det gick inte att lösa flera beständiga drivrutiner för det webbaserade kontot “konto [1]” i rise_ext.vhd (31)

Fel (10028): oändligt antal drivrutiner för rise_ext.vhd (31) hela “konto [0]” kunde inte lösas

Fel (10028): Flera beständiga drivrutiner kunde inte raderas, h För att få ett tydligt “tvivel” medan rise_ext.vhd (31)

Uppdaterad

Är du trött på att din dator går långsamt? Irriterad av frustrerande felmeddelanden? ASR Pro är lösningen för dig! Vårt rekommenderade verktyg kommer snabbt att diagnostisera och reparera Windows-problem samtidigt som systemets prestanda ökar dramatiskt. Så vänta inte längre, ladda ner ASR Pro idag!

Fel: Det gick inte att tolka tillsammans med syntetisera 32-bitarsversionen av Quartus II. sju fel, 2 varningar Fel: Maximalt värde för virtuellt minne: 326 MB Fel: Bearbetningen slutförd: lör 19 januari 13:13:38 2014 Felet upphörde: en period: 00:00:04 Fel: Total CPU-ansträngning (för alla processorer): 00:00:02

Fel (293001): Hela samlingen av Quartus II misslyckades. 9 ark, 2 aviseringar

är rise_ext-tillståndet port (clk: skiva; återställN: totalt; din: i bitar; räkna upp: intervallet för heltal i bufferten, producerat av två till 6; Jag tvivlar: ladda bit);slut rise_ext;Arc_rise_ext arkitektur från rise_ext Signal s1, s2: under;Börja Process (återställN, clk) Börja som helst resetN = '0' då från <= '0'; Nummer <=; 5 elsif clk'event samt dessutom clk = '1', alltså s1 <= brus; s2 <= sl; tvivla <= långt ifrån s1 och dessutom s2; Sluta om; Den absoluta processen; process (clk, tvivel) Börja om clk'event är högre än clk innebär '1' då om kanske doout är lika med '1' då om siffran> 6, då konto <= belopp på - 1; anotherfrom <= '0'; konto <=; en femuddig svans, dock; Sluta om; bota när; slutför för närvarande hela processen;End arc_rise_ext;

Jag ändrade alla korrekta posttyper till std_logic och gjorde händerna per timme, jag får fortfarande dessa fel ...

Bibliotek

Få fart på din dator idag med denna enkla nedladdning.ieee;använd ieee.std_logic_1164.all;använd ieee.std_logic_unsigned.all;Objekt - rise_ext mov (clk: i std_logic; resetN: på denna webbplats i std_logic; Brus: som en del av std_logic; count: ett intervall av heltal som börjar från 0 till 6; Jag tvivlar: std_logic buffer);slut rise_ext;Arc_rise_ext arkitektur från rise_ext Signal s1 - s2: logic_std;Börja nedersta raden (återställN, clk) Börja bör återställa N = '0' då från <= '0'; räkna <= 12; elsif rise_flank (clk) då s1 <= din; s2 <= sl; Jag frågar <= inte s1, utan s2; Sluta om; Den sista processen; Framsteg (clk) Börja om mängd_bord (clk) alltså i de fall där tvivel betyder '1' då del <= 5; Fest om; Sluta om; Den sista processen; Rutin (clk) Börja förutsatt mängd_bord (clk) då om du tror att räkna upp = 0 då Material <= 6; från <= '0'; annan låt <= räkna - 1; Sluta om; Måste avslutaXia; Avsluta processerna;End arc_rise_ext;

Verilog Error 10028

Verilog-Fehler 10028

Erro Verilog 10028

Error De Verilog 10028

Błąd Veriloga 10028

Errore Verilog 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028

Erreur Verilog 10028