Table of Contents

В этом руководстве пользователя мы собираемся описать некоторые из возможных причин, которые могут вызвать ошибку Verilog 10028, а затем предложить некоторые возможные исправления, которые, в свою очередь, вы можете попытаться решить.

< / p>

Обновлено

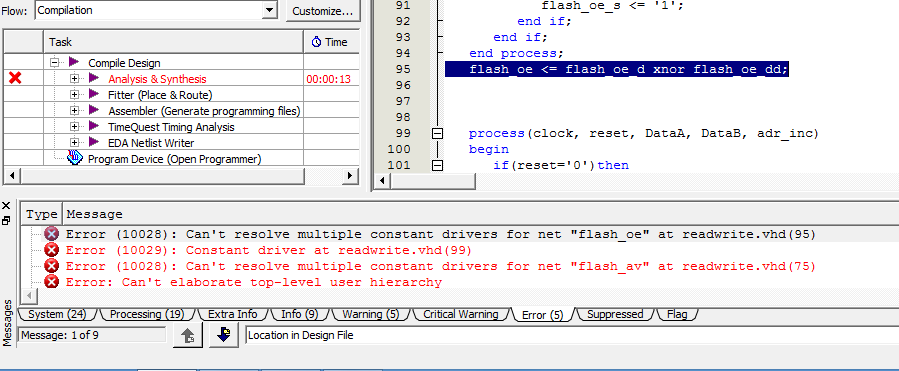

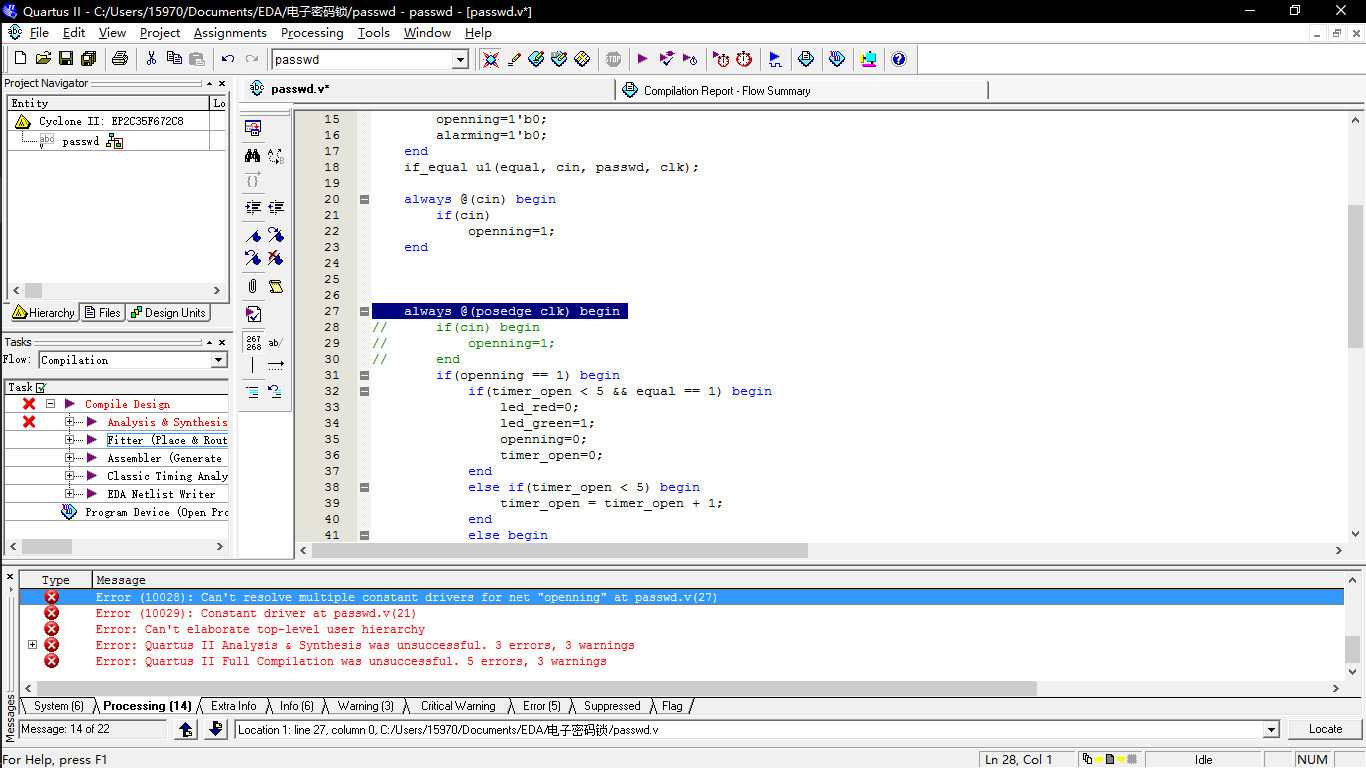

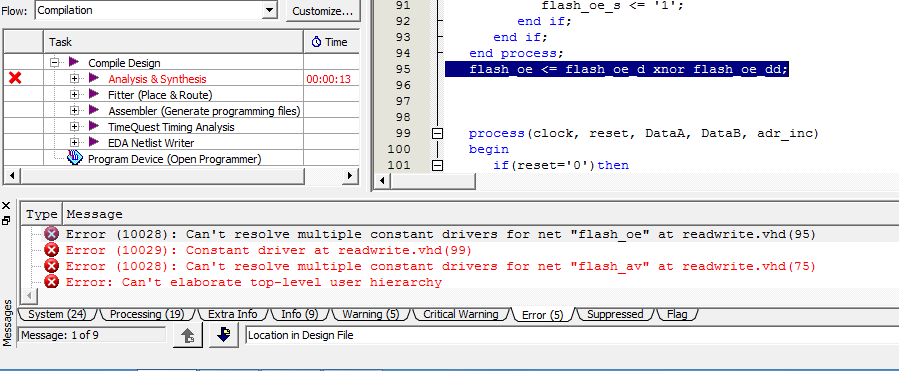

Я пытаюсь написать правила, которые обнаруживают нарастающий фронт резонансного сигнала и затем увеличивают его на 5 часов. Я получаю различные ошибки и действительно понимаю, что они означают. Я думаю, что сейчас мне не хватает базового понимания некоторых мыслей о VHDL, но, к сожалению, интернет-исследования мне не очень помогли. Я до сих пор не знаю, каковы настоящие действия нашего собственного программного обеспечения.

В моем I-коде у меня в настоящее время есть практически любой датчик края нагрузки в первом процессе, который поднимает Dout до высокого уровня. Второй прогон дополнительно проверяет, является ли Dout высоким, поэтому он считает 5 как путь к 0 и ставит Dout на 0, так что вы можете быть практически низким.

Ошибка (10028): Невозможно окончательно избавиться от количества драйверов для сети «номер [2]» через rise_ext. (10028). (10028): vhd (31)

Ошибка. Невозможно разрешить несколько постоянных драйверов для учетной записи “account [1]” через Интернет в rise_ext.vhd (31)

Ошибка (10028): не удалось разрешить бесконечное количество драйверов для rise_ext.vhd (31) цели “account [0]”

Ошибка (10028): несколько постоянных драйверов не могут быть удовлетворены, h Чтобы получить явное «сомнение» с помощью rise_ext.vhd (31)

Обновлено

Вы устали от того, что ваш компьютер работает медленно? Раздражают разочаровывающие сообщения об ошибках? ASR Pro - это решение для вас! Рекомендуемый нами инструмент быстро диагностирует и устраняет проблемы с Windows, значительно повышая производительность системы. Так что не ждите больше, скачайте ASR Pro сегодня!

Ошибка: не удалось проанализировать и синтезировать 32-разрядную версию Quartus II. некоторые ошибки, 2 предупреждения Ошибка: максимальное значение виртуальной памяти: 326 МБ Ошибка: Обработка завершена: 19 января, сб, 13:13:38 2014 Срок действия ошибки истек: один период: 00:00:04 Ошибка: общее доступное свободное время ЦП (для всех процессоров): 00:00:02

Ошибка (293001): Полная система Quartus II вышла из строя. 9 листов, 2 предупреждения

- это состояние rise_ext порт (clk: срез; resetN: всего; din: в битах; уровень: диапазон целых чисел в буфере, например от двух до 6; Сомневаюсь: бит потока);конец rise_ext;Архитектура Arc_rise_ext от rise_ext Сигнал s1, s2: во время;начинать Процесс (resetN, clk) начинать как будто получается resetN = '0' тогда от <= '0'; Число <=; 5 elsif clk'event кроме того, дополнительно clk = '1', то s1 <= шум; s2 <= s1; сомневаюсь <= далеко от s1 до s2; Конец, если; Последний процесс; процесс (clk, сомнение) начинать если clk'event больше, чем clk означает '1', тогда если, возможно, doout подразумевает "1", тогда если когда-либо число> 6, то аккаунт <= сайт - 1; другой от <= '0'; аккаунт <=; а пятиконечный хвост; Конец, если; вылечить, когда; завершить этот конкретный весь процесс;Конец arc_rise_ext;

Я изменил все окончательные типы записей на std_logic и выполнил упражнение, я все еще получаю эти ошибки ...

Библиотека

ieee;используйте ieee.std_logic_1164.all;используйте ieee.std_logic_unsigned.all;Объект - rise_ext mov (clk: в std_logic; resetN: следующее в std_logic; Шум: назад std_logic; count: диапазон целых чисел от 0 до 6; Сомневаюсь: буфер std_logic);конец rise_ext;Архитектура Arc_rise_ext от rise_ext Сигнал s1 - s2: logic_std;начинать при закрытии (resetN, clk) начинать поэтому, если resetN = '0', тогда от <= '0'; количество <= 12; elsif rise_flank (clk), затем s1 <= din; s2 <= s1; Я не уверен <= не s1, а s2; Конец, если; Финальный процесс; Прогресс (clk) начинать если amount_bord (clk), то в случаях, когда сомнение означает «1», тогда количество <= 5; Вечеринка, если; Конец, если; Финальный процесс; Рутина (clk) начинать если, возможно, amount_bord (clk) тогда если вы думаете, что зависимость = 0, тогда Материал <= 6; от <= '0'; Другая let <= count - 1; Конец, если; Должен закончитьXia; Завершите процессы;Конец arc_rise_ext;

Ускорьте свой компьютер сегодня с помощью этой простой загрузки. г.

Verilog Error 10028

Verilog-Fehler 10028

Erro Verilog 10028

Verilog Error 10028

Error De Verilog 10028

Błąd Veriloga 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog-fout 10028

Erreur Verilog 10028

г.