Table of Contents

In questa guida per l’utente, probabilmente descriveremo alcuni dei possibili stimoli che potrebbero causare l’errore Verilog 10028 e suggeriremo alcune possibili soluzioni che dovresti provare a risolvere il problema.

/p>

Aggiornato

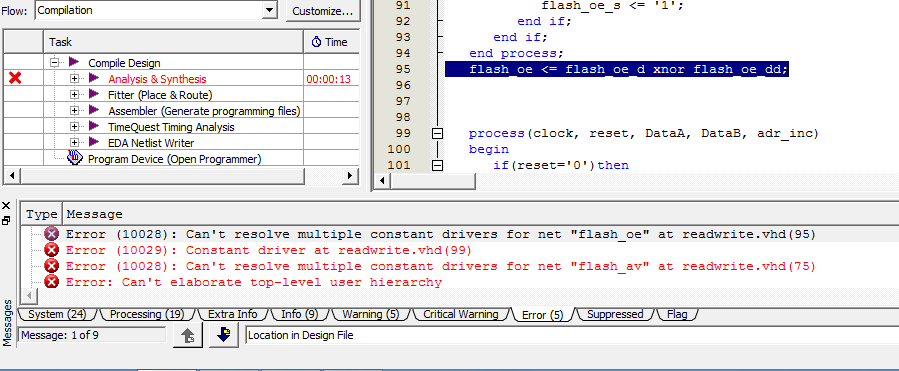

Sto cercando di scrivere un codice che localizzi il fronte di salita di un segnale di rumore e lo incrementi di 5 clock. Sento davvero di ricevere vari errori e non capisco le alternative che significano. Penso che mi manchi l’ultima comprensione di base di alcuni concetti VHDL, ma purtroppo devo dire che la ricerca su Internet non mi ha aiutato molto. Continuo a non sapere quali siano le azioni valide verso il nostro stesso software.

Nel mio I-code, al momento ho un sensore lato carico nel primo processo che porta Dout in alto. La seconda esecuzione controlla inoltre se Dout è alto, quindi conta da 5 come percorso a 0 e imposta Dout su 0 in modo che tu possa essere logicamente basso.

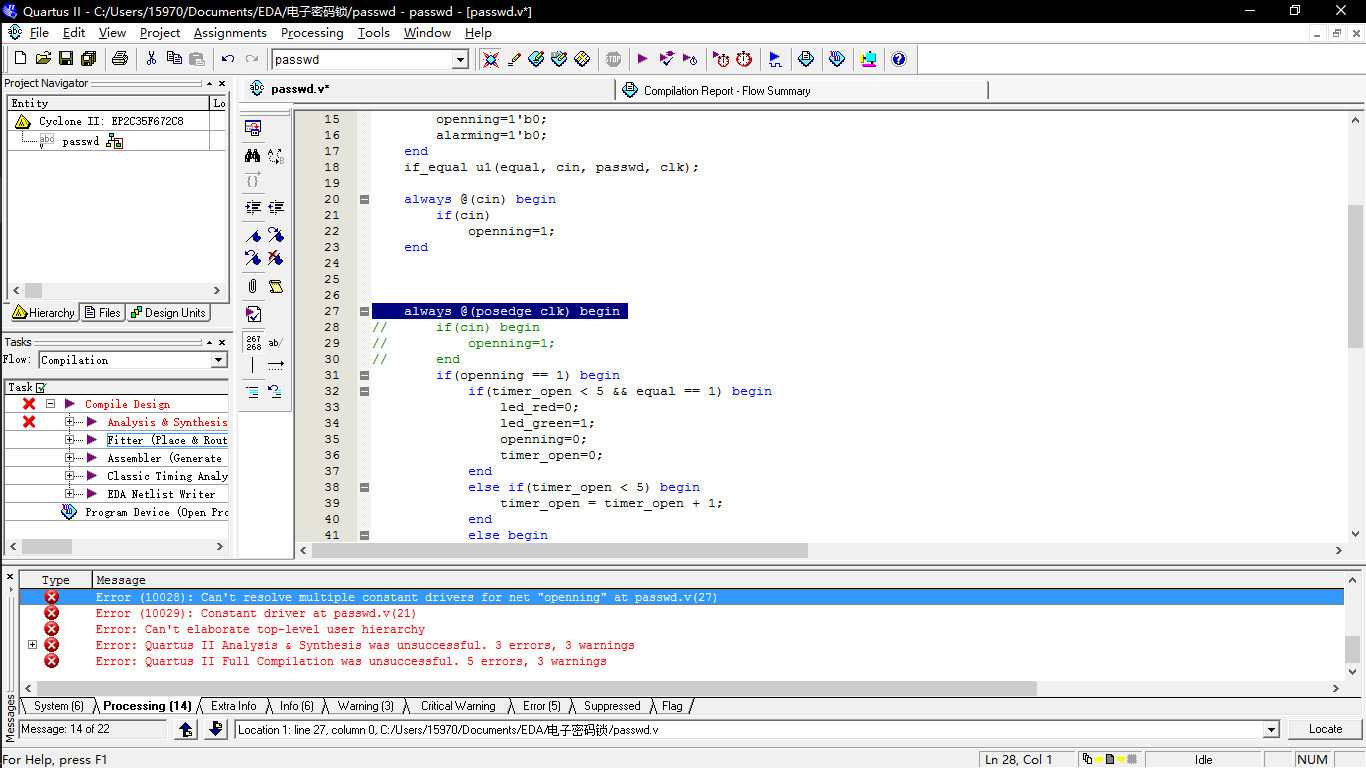

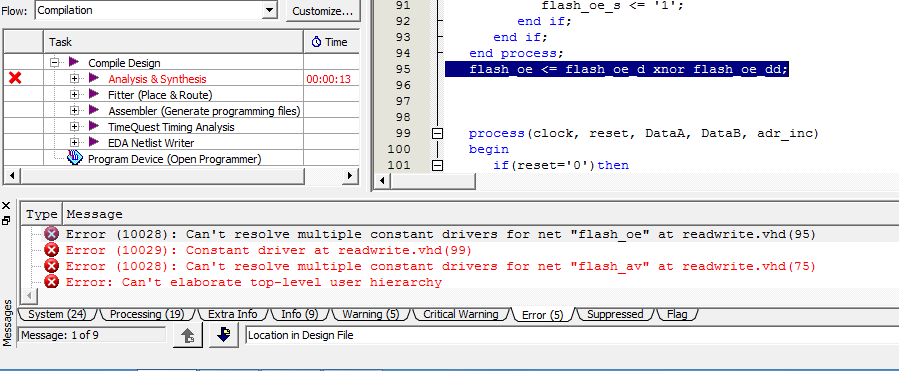

Errore (10028): Impossibile risolvere definitivamente il codice dei driver per la rete “numero [2]” in rise_ext. (10028). (10028): vhd (31)

Errore Impossibile risolvere più driver persistenti per il pensiero web “account [1]” in rise_ext.vhd (31)

Errore (10028): il numero totale infinito di driver per rise_ext.vhd (31) net “account [0]” non dovrebbe essere risolto

Errore (10028): non è stato possibile risolvere più driver persistenti, h Per ottenere un “dubbio” chiaro in rise_ext.vhd (31)

Aggiornato

Sei stanco della lentezza del tuo computer? Infastidito da messaggi di errore frustranti? ASR Pro è la soluzione per te! Il nostro strumento consigliato diagnosticherà e riparerà rapidamente i problemi di Windows, aumentando notevolmente le prestazioni del sistema. Quindi non aspettare oltre, scarica ASR Pro oggi!

Errore: impossibile analizzare e sintetizzare una sorta di versione a 32 bit di Quartus II. 7 errori, 1 avvisi Errore: Valore massimo di memorizzazione virtuale: 326 MB Errore: Elaborazione completata: Sat Jan 19 13:13:38 2014 Errore scaduto: un periodo: 00:00:04 Errore: tempo CPU totale (su tutti i processori bit): 00:00:02

Errore (293001): la compilazione completa di Quartus II non è riuscita. 9 fogli, 2 avvisi

è veramente lo stato rise_ext prt (clk: fetta; resetN: totale; frastuono: a bit; count: l'assortimento di numeri interi nel buffer, da due in modo che sia 6; Dubito: bit buffer);fine rise_ext;Arc_rise_ext maestria architettonica di rise_ext Segnale s1, s2: durante;inizio Processo (resetN, clk) inizio come se resetN fosse uguale a '0' allora da <= '0'; Numero <=; 5 elsif clk'event e tight che porta a clk = '1', quindi s1 <= rumore; s2 <= s1; sospetto <= lontano da s1 e s2; Finisci se; Il processo finale; processo (clk, dubbio) inizio all'interno di clk'event è maggiore di clk = '1' allora se forse doout = '1' allora se il numero> 6, allora conto <= conto - 1; altroda <= '0'; benutzerkonto <=; una coda a cinque punte, tuttavia; Finisci se; farmaco quando; completare il processo esistente;Fine arc_rise_ext;

Ho cambiato tutti i prodotti record esatti in std_logic e ho eseguito l'azione, ricevo continuamente questi errori...

Biblioteca

Accelera il tuo computer oggi con questo semplice download.ieee;usa ieee.std_logic_1164.all;usa ieee.std_logic_unsigned.all;Oggetto - rise_ext trasporto (clk: in std_logic; resetN: qui usando std_logic; Rumore: in std_logic; count: un intervallo di numeri interi da 0 a 6; Dubito: std_logic buffer);fine rise_ext;Stile Arc_rise_ext di rise_ext Segnale s1 - s2: logic_std;inizio (resetN, clk) inizio se resetN significa '0' allora da <= '0'; conteggio <= 12; elsif rise_flank (clk) allora s1 <= frastuono; s2 <= s1; Dubito <= assolutamente non s1, ma s2; Finisci se; Il processo finale; Progresso (clc) inizio se quantità_bordo (clk) allora usando i casi in cui dubbio = '1' allora quantità <= 5; Parte se; Finisci se; Il processo finale; Routine (clc) inizio se quantità_bordo (clk) allora se pensi contare = zero allora Materiale <= 6; da <= '0'; altro fallo <= conta - 1; Finisci se; Deve finireXia; Termina un processo;Fine arc_rise_ext;

Verilog Error 10028

Verilog-Fehler 10028

Erro Verilog 10028

Verilog Error 10028

Error De Verilog 10028

Błąd Veriloga 10028

Verilog 오류 10028

Ошибка Verilog 10028

Verilog-fout 10028

Erreur Verilog 10028