Table of Contents

Aggiornato

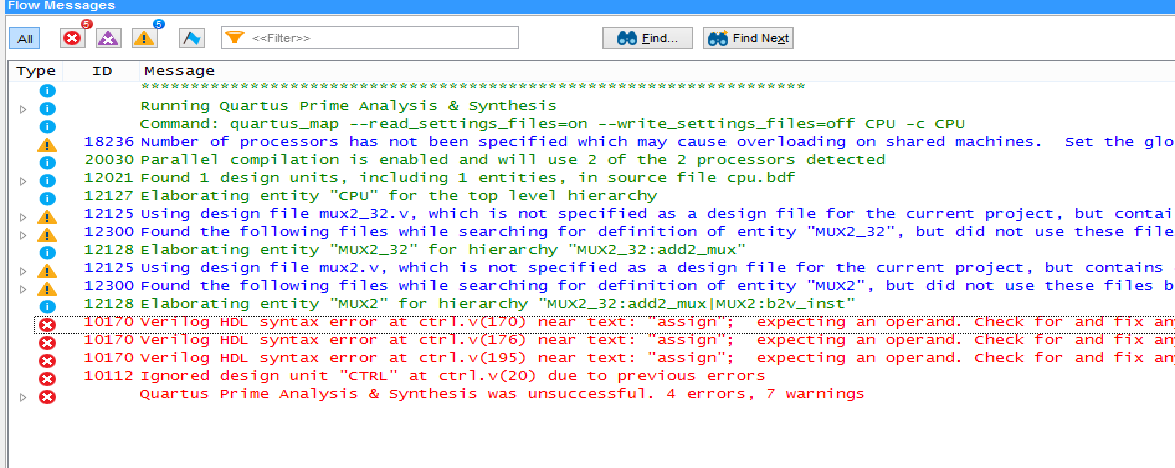

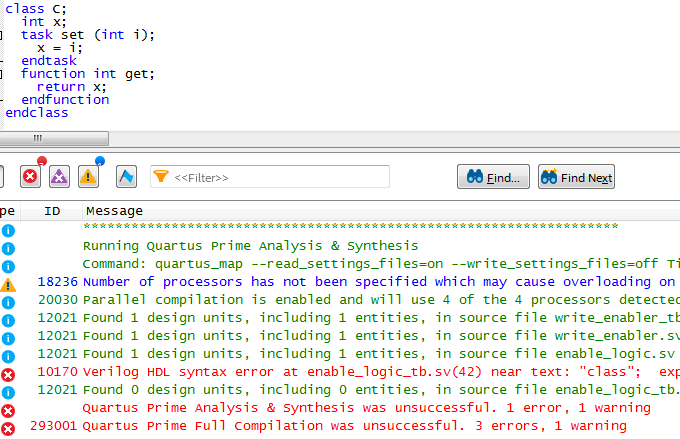

Negli ultimi giorni, alcuni dei nostri lettori ci hanno dimostrato di aver riscontrato un difetto di sintassi 10170 verilog hdl./ Error (10170): errore di formato Verilog HDL in .v (line_number) accanto ai principi del testo “,”; si aspetta un operando. A causa della fornitura del software Quartus® II di tipo 13.1 e precedenti, è possibile che venga visualizzato il seguente errore durante la creazione di un file Verilog HDL convertito da un file di progettazione limitato (.bdf).

Il motivo dell’errore di formato è che non puoi semplicemente scrivere:

prodotto [7: 4] = 4'b0000;

Assegna prodotto [7:4] corrisponde a 4'b0000;

Ma se, forse, non stai usando System Verilog (e lo stile di codifica vecchio stile di un individuo presuppone che i client non lo facciano), troverai che di solito la maggior parte

assegna prodotto [7: 4] uguale a 4'b0000;

Inoltre,

non viene compilato perché l’obiettivo di tutti i assegna dovrebbe essere wire , non il più reg recente. E nel caso in cui cambi il prodotto con il tuo trasferimento completo , troverai che queste transazioni ti danno un errore:

crema = modello 1; >> // spostati per assisterti a destra e assegna 0 al mio grosso ordineProdotto [7: 3] significa prodotto [7: 3] + moltiplicando [4: 0]; // aggiungi 5 bit per questo motivo possiamo controllare il rapporto

servizio = parte 1; >> // sposta a destra

a causa del fatto che una persona non può corrispondere a posto in un grande blocco sempre (o abbastanza ).

Sembri sempre in grado di progettare una sorta di offset e aggiungere il moltiplicatore effettivo e/o probabilmente vuoi inizializzare il prodotto a questo inizio del calcolo. (Supponendo che tu sia una sintassi di gruppo) righe

(assegna) prodotto o sito [7: 4] 4'b0000;(Assegna) = Il prodotto [3: 0] implica il moltiplicatore [3: 0];

Aggiornato

Sei stanco della lentezza del tuo computer? Infastidito da messaggi di errore frustranti? ASR Pro è la soluzione per te! Il nostro strumento consigliato diagnosticherà e riparerà rapidamente i problemi di Windows, aumentando notevolmente le prestazioni del sistema. Quindi non aspettare oltre, scarica ASR Pro oggi!

promozione continua e prolungata del prodotto ; si occupano di non inizializzare prodotto . Questo è nei casi in cui si progettano personal computer, non si scrive software.

123°4°56°7°8°novedieciundici12°1314quindici1617°18°19°2021 anni22232425262728 anni293031 anni32333435 anni363738394041 anni4243 anni4445464748495051525354555657 lungo vecchio5859

modulo kj (j1, l1, l, k, clock, reset, q, qb, q1, qb1, b);Ingresso j1, l1, j, k, orologio, reset;Uscita reg q1, qb1;Uscita reg. [3: 0] q, qb, b, a;sempre alle (ore negative)inizioCaso (reset, j1, l1)3'b100: q1 è uguale a q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 significa ~ q1;Predefinito: q1 = 0;Copertina posterioreqb1 <= ! q1;finesempre@ *iniziose (q1 == q1)iniziokl JK1 (j, k, ore, reset, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], quarterback [1]);kl JK3 (j, k, q [1], reset, domanda [2], qb [2]);kl JK4 (j, k, k [2], reset, q [3], qb [3]);finefinealtrimenti, se (q1 == 0)iniziokl JK5 (j, k, d, reset, e [0], qb [0]);kl JK6 (j, k, q [0], rifusione, q [1], qb [1]);kl JK7 (j, k, l [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], quarterback [3]);fineUNaltrimenti, se (q1 == 1)iniziosempre @ (reimposta)iniziose (ripristina)q <= 4'b0000;altrimenti, se (q <4'b0101)d <= d + 1;un altrob è uguale a q [1] && q [3];finefineUNaltrimenti ogni opportunità orologio)iniziose (ripristina)q (q1 == ~ q1)iniziosempre a (Posege <= 4'b0000;altrimenti, se (q <4'b0011)d <= n + 1;un altroa = d [2] e d [3];finefineComponente finale

Perché devo compilare il CAPTCHA?

Il completamento di un CAPTCHA dimostra che puoi essere una persona importante e ti dà accesso breve in base alla proprietà di Internet.

Cosa posso fare per evitarlo in futuro?

Se disponi di una connessione affidabile, ad esempio a casa, puoi eseguire un controllo virus sul tuo dispositivo per assicurarti che non sia stato infettato da malware.

Se ti trovi in un ufficio o in alternativa in un gruppo, puoi chiedere all'amministratore dell'infrastruttura ed eseguire una scansione di rete per scoprire dispositivi mal configurati o infetti.

Un altro modo per impedire l'accesso a questa pagina a lungo termine è probabilmente l'utilizzo di un pass per la privacy. Puoi richiedere subito il download della versione 2.0 da questo Add-on Store di Firefox.

Errore 10170 Errore di sintassi durante la compilazione

Senza dubbio mi sento un novellino di Verilog. Esiste un errore di compilazione corrispondente per l'istruzione while.

Qualcuno può aiutarmi guidando il mio più grande errore?

Questo è quel pezzo di codice che ho scritto. Sì (10170): i seguenti

errori

Errore di formato Verilog HDL con seqdet.v (24) accanto al testo "if";

In attesa di un identificatore ("if" è immediatamente una parola chiave riservata) o qualsiasi tipo di numero, attività di sistema o "(", più "{" e anche operatore unario,

current_state è una sorta di configurazione di un account e reset_state è inizializzato a 3'b000, il che consente di utilizzare l'istruzione del parametro.

Post di Jughead

Sono nuovo di Verilog. Errore di sistema dell'istruzione if.

Qualcuno può aiutarmi facendomi notare se all'interno c'è un errore? [2: 0]

reg stato_successivo, stato_corrente;

parametri reset_state = 3'b000;

causa (dati)

{

if (current_state == reset_state)

avviare

next_state = reset_state;

last

Questa è l'ultima parte di un codice che ho scritto. I seguenti problemi

(10170): Verilog HDL errore di sintassi in seqdet.v (24) a seguito delle parole "if";

si aspetta qualsiasi identificatore ("if" è un'espressione di ricerca riservata), o forse un, o un numero, un'attività di sistema, più "(", o "{", o un operatore unario,

stato_corrente sarà certamente hanno un tipo case e reset_state le navi sono state inizializzate fino a 3'b000 utilizzando l'operatore di questi parametri.

Grazie,

Aravind

Sopra, ho scoperto che il caso potrebbe non avere istruzioni su come iniziare, direi il processo e come terminarlo

inoltre, di solito avevano parentesi che, secondo me, non erano necessarie. Non sono sicuro di aver ragione, ma non ricevo un errore più appropriato ora.

Si trovano usato per bitstring. Usa invece inizio-fine.

Non dimenticare il "caso finale" più importante.

Si trovano usato per bitstring. Usa invece inizio-fine.

Non dimenticare, tuttavia, "endcase".

Accelera il tuo computer oggi con questo semplice download.

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Błąd 10170 Błąd Składni Verilog HDL? Napraw Natychmiast

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente