Table of Contents

Zaktualizowano

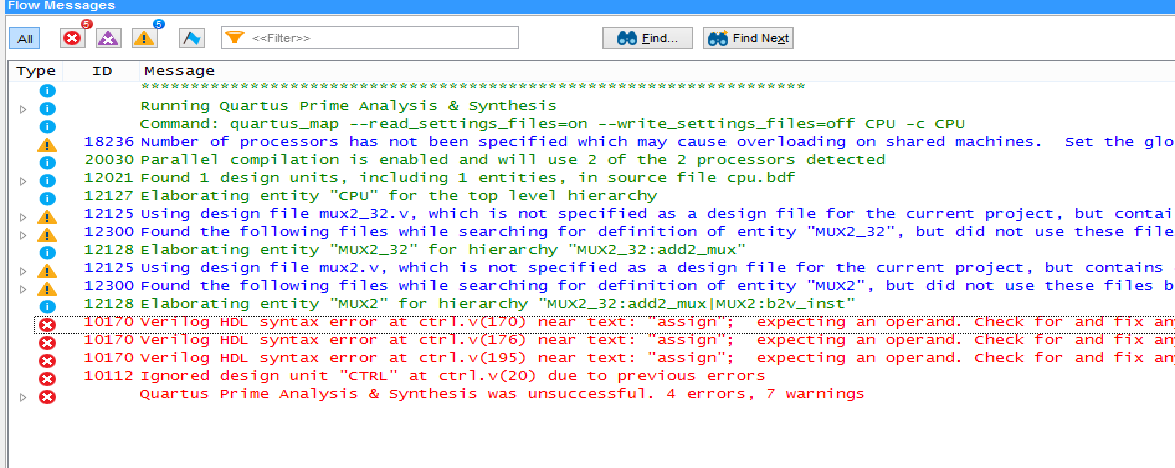

W ciągu kilku powyższych dni niektórzy z naszych czytelników powiedzieli nam, że napotkali problemy ze składnią 10170 verilog hdl./ Błąd (10170): błąd formatu Verilog HDL w .v (numer_linii) obok wiadomości tekstowych “,”; oczekuje operandu. Ze względu na obawy związane z oprogramowaniem Quartus® II typu 13.1 i powyżej, podczas tworzenia pliku Verilog HDL przekonwertowanego z pliku projektu niewidocznego (.bdf) może pojawić się następujący błąd.

Przyczyną błędu formatu jest to, że nie można po prostu napisać:

produkt [7: 4] = 4'b0000;

Przypisz produkt [7: 4] odpowiada 4'b0000;

Ale jeśli nie używasz System Verilog (a twój podstawowy staromodny styl kodowania zakłada, że klienci tego nie robią), znajdziesz, ponieważ większość

przypisz produkt [7: 4] równa się 4'b0000;

Ponadto

nie kompiluje się, ponieważ celem przypisania powinien być przewód , a nie najnowszy rej. . A gdy zmienisz produkt na rzeczywisty pełny transfer , znajdziesz dokładnie, kto w tych transakcjach powoduje błąd:

narzędzie = model 1; >> // przesuń się za Ciebie w prawo i przypisz 0 do mojego ekstra wysokiego zamówieniaIloczyn [7:3] oznacza iloczyn [7:3] + mnożnik [4:0]; // dodaj 5 bitów, o których mówi się, że możemy kontrolować raport

marka = część 1; >> // przesuń w prawo

biorąc pod uwagę fakt, że dana osoba nie może dopasować sznurka w dużym bloku zawsze (lub wstępny ).

Zawsze wydaje Ci się, że możesz zaprojektować jakiś rodzaj przesunięcia i dodać odpowiedni mnożnik i/lub prawdopodobnie chcesz zainicjować produkt na początku obliczeń. (Zakładając, że masz składnię grupową) wiersze

(przypisanie) produkt lub firma [7: 4] 4'b0000;(Przypisz) = Iloczyn [3: 0] implikuje Mnożnik [3: 0];

Zaktualizowano

Czy masz dość powolnego działania komputera? Denerwują Cię frustrujące komunikaty o błędach? ASR Pro to rozwiązanie dla Ciebie! Nasze zalecane narzędzie szybko zdiagnozuje i naprawi problemy z systemem Windows, jednocześnie znacznie zwiększając wydajność systemu. Więc nie czekaj dłużej, pobierz ASR Pro już dziś!

ciągła i stopniowa promocja produktu ; nie powinny inicjować produktu . Właśnie w tym miejscu projektujesz komputery osobiste, a nie piszesz oprogramowanie.

123rd4.56.7thósmydziewięćdziesięćjedenaście12.1314.piętnaście1617.18.19.20.21 lat22.232425262728 lat2930.31 rok32333435 lat363738394041 lat4243 lata4445464748495051525354555657 wielu starych5859

moduł kj (j1, l1, s, k, zegar, reset, q, qb, q1, qb1, b);Wejście j1, l1, j, k, zegar, reset;Rejestr wyjściowy q1, qb1;Reg wyjście. [3:0] q, qb, b, a;zawsze o (godzinach ujemnych)rozpocząćSprawa (reset, j1, l1)3'b100: q1 oznacza q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 implikuje ~ q1;Domyślnie: q1 = 0;Tylna pokrywaqb1 <= ! q1;kończyć sięzawsze@ *rozpocząćjeśli (q1 == q1)rozpocząćkl JK1 (j, k, godziny, reset, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], rozgrywający [1]);kl JK3 (j, k, q [1], reset, n [2], qb [2]);kl JK4 (j, k, e [2], reset, q [3], qb [3]);kończyć siękończyć sięw przeciwnym razie, jeśli (q1 == 0)rozpocząćkl JK5 (j, k, d, reset, x [0], qb [0]);kl JK6 (j, k, q [0], przekształcenie, q [1], qb [1]);kl JK7 (j, k, x [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], rozgrywający [3]);kończyć sięAinaczej, jeśli (q1 == 1)rozpocząćzawsze @ (resetuj)rozpocząćjeśli (zresetuj)q <= 4'b0000;w przeciwnym razie, jeśli (q <4'b0101)d <= d + 1;inneb równa się q [1] && q [3];kończyć siękończyć sięAw przeciwnym razie każdy dostępny zegar czasu wolnego)rozpocząćjeśli (zresetuj)q (q1 == ~ q1)rozpocząćzawsze na (Posege <= 4'b0000;w przeciwnym razie, jeśli (q <4'b0011)d <= r + 1;innea = d [2] i d [3];kończyć siękończyć sięJednostka końcowa

Dlaczego muszę wypełniać CAPTCHA?

Wypełnienie CAPTCHA dowodzi, że jesteś ważną osobą i zapewnia tymczasowy dostęp w oparciu o posiadanie Internetu.

Co mogę zrobić, aby tego uniknąć w przyszłości?

Jeśli masz niezawodne połączenie, na przykład w domu, możesz przeprowadzić badanie wirusów na swoim urządzeniu, aby upewnić się, że zwykle nie jest ono zainfekowane złośliwym oprogramowaniem.

Jeśli jesteś w biurze, a także w grupie, możesz poprosić administratora programu i uruchomić skanowanie sieci, aby wykryć źle skonfigurowane lub zainfekowane urządzenia.

Innym sposobem na uniemożliwienie dostępu do tej strony w dłuższej perspektywie jest prawdopodobnie użycie przepustki prywatności. Możesz teraz poprosić o pobranie wersji 2.0 z tego sklepu z dodatkami do Firefoksa.

Błąd 10170 Błąd składni podczas kompilacji

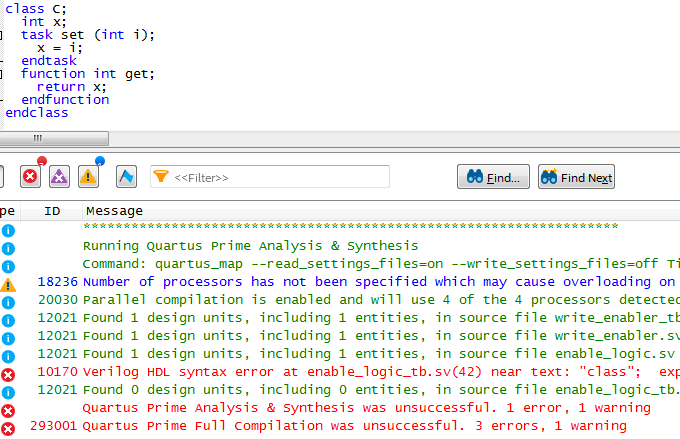

Niesamowicie czuję się jak nowicjusz w Verilog. W przypadku tej instrukcji występuje odpowiedni błąd kompilacji.

Czy ktoś może mi pomóc w wykryciu mojego największego błędu?

To jest nowy fragment kodu, który napisałem. Tak (10170): następujące

błędy

Błąd formatu Verilog HDL z sekcją seqdet.v (24) obok tekstu „jeśli”;

Oczekiwanie na identyfikator ("if" jest wyraźnie zastrzeżonym słowem kluczowym) lub dowolny rodzaj zdarzenia, zadanie systemowe lub "(", plus "{" oraz operator jednoargumentowy,

current_state jest rodzajem zakupu, a reset_state jest inicjowany do 3'b000, co jest osiągalne dla instrukcji parametru, która ma być użyta.

Post przez Jughead

Jestem nowy w Verilog. Błąd systemowy instrukcji if.

Czy ktoś może mi pomóc, wskazując na poważną pomyłkę? [2: 0]

reg następny_stan, aktualny_stan;

parametry stan_resetowania = 3'b000;

wystąpienie (dane)

{

if (current_state == reset_state)

zaczyna się

next_state = reset_state;

mety

To jest ostatnia część ich kodu, którą spisałem. Następujące wady

(10170): Verilog HDL błąd składni w seqdet.v (24) najpóźniej do słów "if";

oczekuje określonego identyfikatora ("if" jest zarezerwowanym wyrażeniem wyszukiwania) lub liczby, zadania systemowego, lub może to być "(" lub "{" lub operator jednoargumentowy,

current_state może również mieć typ case, a miejsca reset_state zostały zainicjowane do 3'b000 przy użyciu operatora parametrów.

Dzięki,

Aravind

Powyżej dowiedziałem się, że w złożonej sprawie nie było instrukcji, jak rozpocząć konkretny proces i jak go zakończyć

oraz zwykle zawierały nawiasy, które według mnie nie były potrzebne. Nie jestem pewien, czy mam rację, ale teraz nie otrzymuję pożądanego błędu.

Są położone używany do bitstringu. Zamiast tego użyj początku-końca.

Nie zapomnij o aktualnym "końcu".

Są położone używany do bitstringu. Zamiast tego użyj początku-końca.

Nie zapomnij jednak o „końcu”.

Przyspiesz swój komputer już dziś dzięki temu prostemu pobieraniu.

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Errore 10170 Verilog HDL Errore Di Sintassi? Riparare Immediatamente

Fehler 10170 Verilog HDL-Syntaxfehler? Sofort Reparieren

Fout 10170 Verilog HDL-syntaxisfout? Onmiddellijk Repareren

오류 10170 Verilog HDL 구문 오류? 즉시 수리

Erreur 10170 Erreur De Syntaxe Verilog HDL ? Réparer Immédiatement

Fel 10170 Verilog HDL -syntaxfel? Reparera Omedelbart

Erro 10170 Erro De Sintaxe Verilog HDL? Repare Imediatamente

Ошибка 10170 синтаксическая ошибка Verilog HDL? Немедленно отремонтируйте

Error 10170 ¿Error De Sintaxis De Verilog HDL? Reparar Inmediatamente